Display timing: Difference between revisions

Jump to navigation

Jump to search

mNo edit summary |

No edit summary |

||

| (6 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

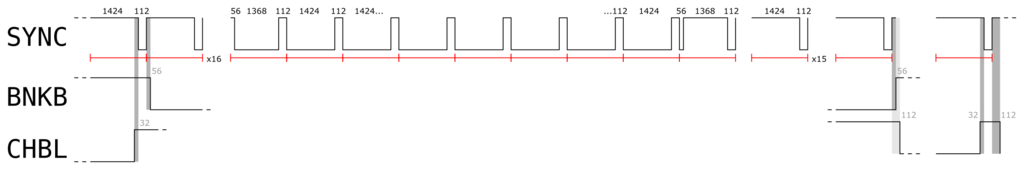

In both NTSC or PAL mode, the full display is always 384 * 264 pixels. | |||

In NTSC mode, the display is | |||

See [[frame size]] for the '''active''' display size. | |||

'''mclk''' refers to the 24MHz master [[clock]]. A pixel lasts 4 mclk. | |||

Notes: After /RESET goes high, SYNC goes high after 1399 mclk. | |||

[[File:Sync_timing.png|1024px]] | |||

{{Sig|CHBL|CHBL}} is the horizontal blanking signal, it tells {{Chipname|NEO-B1}} to output color 0 of [[palettes|palette]] 0, which is the [[palettes|reference color]]. | |||

{{Sig|BNKB|BNKB}} is the vertical blanking signal, it forces the [[video DAC]] inputs to 0. | |||

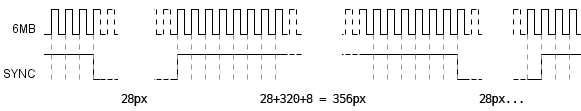

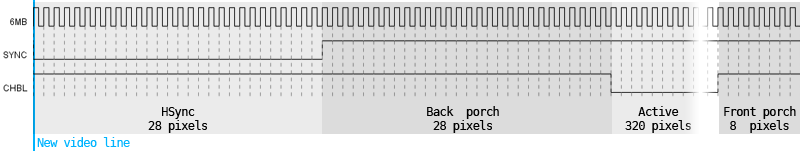

=Horizontal timing= | |||

[[File:Timing_video_lines.png]] | |||

[[File:Timing_video_hblank.png]] | |||

* 112 mclks (28px) horizontal sync pulse | |||

* 112 mclks (28px) back porch | |||

* 1280 mclks (320px) active display | |||

* 32 mclks (8px) front porch | |||

* 32 + 112 + 112 = 256 mclks (64px) horizontal blanking | |||

* 32 + 112 + 112 + 1280 = 1536 mclks (384px) total per scanline | |||

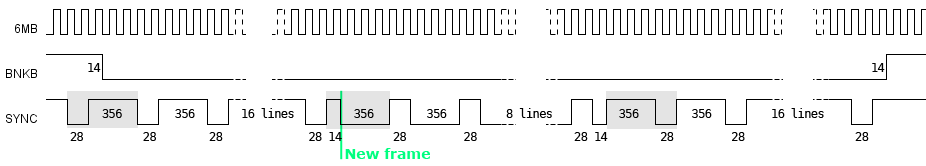

[[File:Timing_video_vblank.png]] | |||

BNKB (blanking to 0V) changes state 14px after H-sync (middle of the back porch) | |||

=Vertical timing= | |||

Corrected from and added on from mvstech.txt (by Charles MacDonald). | |||

There are 264 scanlines per frame: | |||

* 8 scanlines vertical sync pulse | |||

* 16 scanlines top border (active in PAL, blanked in NTSC) | |||

* 224 scanlines active display | |||

* 16 scanlines bottom border (active in PAL, blanked in NTSC) | |||

Upper 9 bits of register {{Reg|REG_LSPCMODE}}: | |||

* $0F8~$0FF : Vertical sync (8px) | |||

* $100~$10F : Top border (16px) | |||

* $110~$1EF : Active display (224px) | |||

* $1F0~$1FF : Bottom border (16px) | |||

=Frame timing= | |||

See [[framerate]]. | |||

[[Category:Video system]] | [[Category:Video system]] | ||

Revision as of 09:38, 19 March 2017

In both NTSC or PAL mode, the full display is always 384 * 264 pixels.

See frame size for the active display size.

mclk refers to the 24MHz master clock. A pixel lasts 4 mclk.

Notes: After /RESET goes high, SYNC goes high after 1399 mclk.

CHBL is the horizontal blanking signal, it tells NEO-B1 to output color 0 of palette 0, which is the reference color.

BNKB is the vertical blanking signal, it forces the video DAC inputs to 0.

Horizontal timing

- 112 mclks (28px) horizontal sync pulse

- 112 mclks (28px) back porch

- 1280 mclks (320px) active display

- 32 mclks (8px) front porch

- 32 + 112 + 112 = 256 mclks (64px) horizontal blanking

- 32 + 112 + 112 + 1280 = 1536 mclks (384px) total per scanline

BNKB (blanking to 0V) changes state 14px after H-sync (middle of the back porch)

Vertical timing

Corrected from and added on from mvstech.txt (by Charles MacDonald).

There are 264 scanlines per frame:

- 8 scanlines vertical sync pulse

- 16 scanlines top border (active in PAL, blanked in NTSC)

- 224 scanlines active display

- 16 scanlines bottom border (active in PAL, blanked in NTSC)

Upper 9 bits of register REG_LSPCMODE:

- $0F8~$0FF : Vertical sync (8px)

- $100~$10F : Top border (16px)

- $110~$1EF : Active display (224px)

- $1F0~$1FF : Bottom border (16px)

Frame timing

See framerate.