NEO-257: Difference between revisions

Jump to navigation

Jump to search

mNo edit summary |

m (→Pinout) |

||

| Line 39: | Line 39: | ||

== Pinout == | == Pinout == | ||

Information provided by Channelmaniac. | Information provided by Channelmaniac. '''Some pins marked as GND could be "enable" pins'''. | ||

* A*, B*: Inputs | |||

* Y*: Outputs | |||

* 17 SELECT: A if low, B if high | |||

* 18 is an active low output enable for Y0~Y7 | |||

* 33 and 34 are probably ORed together to provide an active low output enable for Y8~Y15 | |||

* 35 is an active high enable for entire chip | |||

[[Category:Chips]] | [[Category:Chips]] | ||

Revision as of 10:13, 29 September 2016

| |

| Package | QFP64R |

| Manufacturer | |

| First use | 1990 ? |

| Used on | MV2B... |

Four "74HC257" quad 2-to-1 multiplexers with some common select lines and output enables. Makes 16 switches in one chip (32 inputs, 16 outputs).

Used in dual slot MVS systems to switch between carts.

Select signal comes from one of the "SLOT" outputs of NEO-F0 ?

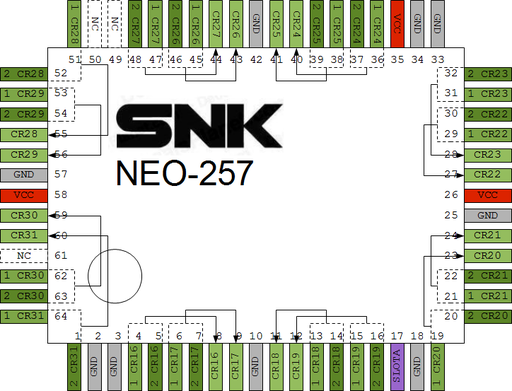

MV2B @ L4 pinout

Used to switch the upper 16 bits of the sprite graphics bus.

OpenOffice Draw file: File:Neo-257 L4.odg

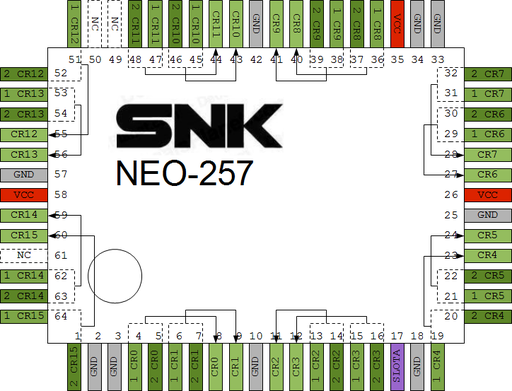

MV2B @ K4 pinout

Used to switch the lower 16 bits of the sprite graphics bus.

OpenOffice Draw file: File:Neo-257 K4.odg

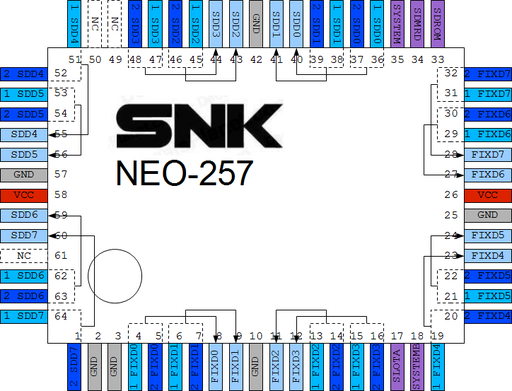

MV2B @ J11 pinout

Used to switch between the onboard SM1 ROM / game M1 ROM, and onboard SFIX ROM / game S ROM.

OpenOffice Draw file: File:Neo-257 J11.odg

Pinout

Information provided by Channelmaniac. Some pins marked as GND could be "enable" pins.

- A*, B*: Inputs

- Y*: Outputs

- 17 SELECT: A if low, B if high

- 18 is an active low output enable for Y0~Y7

- 33 and 34 are probably ORed together to provide an active low output enable for Y8~Y15

- 35 is an active high enable for entire chip