NEO-B1: Difference between revisions

m (Added buffer size) |

m (removed note because pinout is corrected) |

||

| (6 intermediate revisions by 2 users not shown) | |||

| Line 5: | Line 5: | ||

|date=1992 ? | |date=1992 ? | ||

|gates= | |gates= | ||

|used_on={{PCB|NEO-AES3-4}}... | |used_on={{PCB|NEO-AES3-4 board|NEO-AES3-4}}... | ||

}} | }} | ||

| Line 16: | Line 16: | ||

Both [[fix layer|fix]] graphics from the [[S ROM]] and serialized sprite graphics from the [[C ROM]]s are fed to NEO-B1 for display on screen via 2 pairs of alternating line buffers. Sprite graphics come from the C ROM multiplexer ({{Chipname|NEO-ZMC2}}, {{Chipname|PRO-CT0}} or {{Chipname|NEO-CMC}}), while fix graphics come directly from the currently enabled fix ROM. Two pixels are written at a time. | Both [[fix layer|fix]] graphics from the [[S ROM]] and serialized sprite graphics from the [[C ROM]]s are fed to NEO-B1 for display on screen via 2 pairs of alternating line buffers. Sprite graphics come from the C ROM multiplexer ({{Chipname|NEO-ZMC2}}, {{Chipname|PRO-CT0}} or {{Chipname|NEO-CMC}}), while fix graphics come directly from the currently enabled fix ROM. Two pixels are written at a time. | ||

Sprite rendering is done in the internal [[line buffers]]. | |||

The chip outputs the [[palette RAM]] address to select colors for pixel output. The data output of the palette RAM is latched by a pair of 8bit registers, which in turn feed the [[video DAC]]. The NEO-B1 handles address bus switching between the [[68k]] bus and palette RAM. Priority is always given to the 68k which results in harmless display glitches when games access palette RAM during active display. | The chip outputs the [[palette RAM]] address to select colors for pixel output. The data output of the palette RAM is latched by a pair of 8bit registers, which in turn feed the [[video DAC]]. The NEO-B1 handles address bus switching between the [[68k]] bus and palette RAM. Priority is always given to the 68k which results in harmless display glitches when games access palette RAM during active display. | ||

| Line 28: | Line 28: | ||

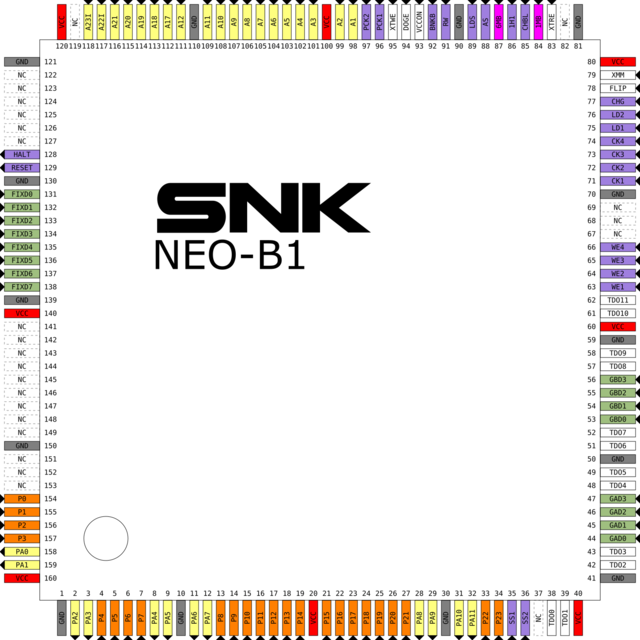

=Pinout= | =Pinout= | ||

{{Pinout|NEO-B1|640}} | |||

=Signals= | =Signals= | ||

*A1~A21: [[68k]] address bus | *A1~A21, A22I, A23I: [[68k]] address bus and modified upper lines | ||

*FIX0~FIX7: Fix ROM data bus | *FIX0~FIX7: Fix ROM data bus | ||

*PCK1/PCK2: Latch signals | *PCK1/PCK2: Latch signals coming from {{Chipname|LSPC2-A2}} | ||

*PA0~PA11: Palette RAM address bus | *PA0~PA11: Palette RAM address bus | ||

*GAD0~GAD3, GBD0~GBD3: Sprite pixel data (2 pixels) | *GAD0~GAD3, GBD0~GBD3: Sprite pixel data (2 pixels) | ||

* | *CK1~CK4: Clocks for each buffer | ||

*WE1~WE4: Write enable for | *WE1~WE4: Write enable for each buffer | ||

*SS1/SS2: Mode select for each pair of buffers | |||

*SS1/SS2: | *LD1/LD2: Buffer address reload signals | ||

*LD1/LD2: | *TMS0: Buffer order selection | ||

*TMS0: | *DOGE: [[Watchdog]] enable (internal pullup) | ||

*DOGE: Watchdog enable (internal pullup) | *FLIP: Flip display horizontally ? Always tied to ground | ||

*XMM, XTRE, XTWE: Test mode enable, direct read and write signals | |||

*TDO0~TDO11: Line buffers test data output | |||

*VCCON: [[Reset]] signal | |||

[[Category:Chips]] | [[Category:Chips]] | ||

Latest revision as of 14:42, 21 May 2020

| |

| Package | QFP160 |

| Manufacturer | |

| First use | 1992 ? |

| Used on | NEO-AES3-4 board... |

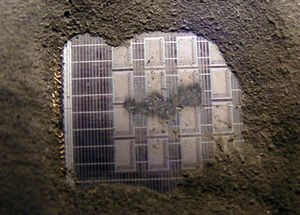

The NEO-B1 chip is found in second generation cartridge-based systems.

Graphics

Both fix graphics from the S ROM and serialized sprite graphics from the C ROMs are fed to NEO-B1 for display on screen via 2 pairs of alternating line buffers. Sprite graphics come from the C ROM multiplexer (NEO-ZMC2, PRO-CT0 or NEO-CMC), while fix graphics come directly from the currently enabled fix ROM. Two pixels are written at a time.

Sprite rendering is done in the internal line buffers.

The chip outputs the palette RAM address to select colors for pixel output. The data output of the palette RAM is latched by a pair of 8bit registers, which in turn feed the video DAC. The NEO-B1 handles address bus switching between the 68k bus and palette RAM. Priority is always given to the 68k which results in harmless display glitches when games access palette RAM during active display.

Watchdog

The watchdog is integrated into NEO-B1. HALT and RESET are generated by this chip on power-on and whenever the 68k fails to kick the watchdog in time. The write to REG_DIPSW is decoded on the chip instead of using a signal from NEO-C1.

Watchdog can be disabled by bringing pin 94 DOGE to ground (J2 jumper on main board).

Pinout

Signals

- A1~A21, A22I, A23I: 68k address bus and modified upper lines

- FIX0~FIX7: Fix ROM data bus

- PCK1/PCK2: Latch signals coming from LSPC2-A2

- PA0~PA11: Palette RAM address bus

- GAD0~GAD3, GBD0~GBD3: Sprite pixel data (2 pixels)

- CK1~CK4: Clocks for each buffer

- WE1~WE4: Write enable for each buffer

- SS1/SS2: Mode select for each pair of buffers

- LD1/LD2: Buffer address reload signals

- TMS0: Buffer order selection

- DOGE: Watchdog enable (internal pullup)

- FLIP: Flip display horizontally ? Always tied to ground

- XMM, XTRE, XTWE: Test mode enable, direct read and write signals

- TDO0~TDO11: Line buffers test data output

- VCCON: Reset signal