NEO-E0

MVS specific chip.

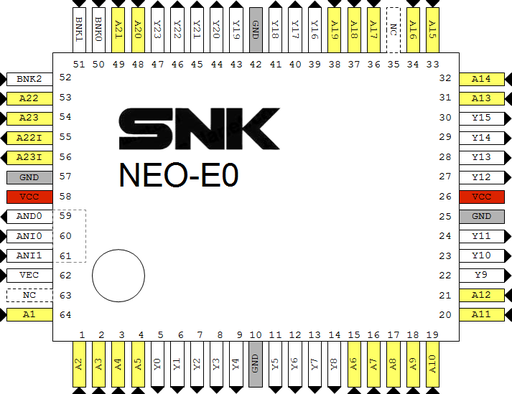

BIOS vector table swapping

When 68k A8~A23 = 0 and the BIOS's vector table is chosen (by using REG_SWPBIOS or REG_SWPROM), A22I~A23I outputs are set to 1. This makes the address appear to address decoding chips as a BIOS access instead of a P ROM access.

On the AES, the AND gate is used for /SROMOE from /SROMOEL AND /SROMOEU.

MV2B @ G2 pinout

|

OpenOffice Draw file: File:Neo-e0 mv2b G2.odg |

|

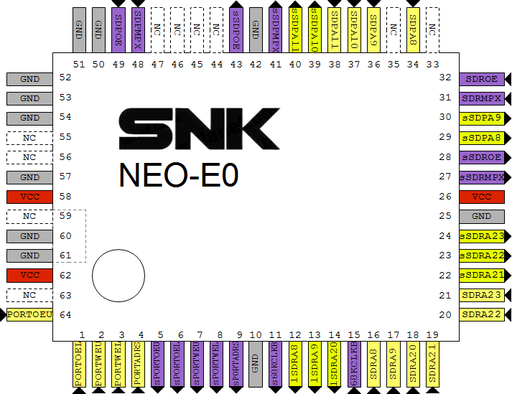

MV2B @ F7 pinout

|

OpenOffice Draw file: File:Neo-e0 mv2b F7.odg |

Acts just as a buffer.

|

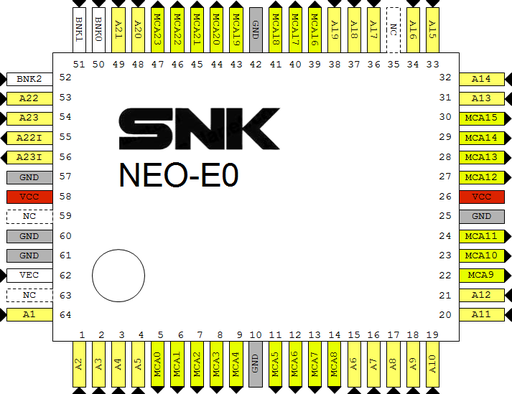

Pinout

|

OpenOffice Draw file: File:Neo-e0.odg |

|