NEO-I0: Difference between revisions

Jump to navigation

Jump to search

m (ChipInfo) |

No edit summary |

||

| (4 intermediate revisions by 2 users not shown) | |||

| Line 5: | Line 5: | ||

|date=1990 ? | |date=1990 ? | ||

|gates= | |gates= | ||

|used_on={{PCB|MV2B}} ... | |used_on={{PCB|MV2B}} {{PCB|MV1-1}} ... | ||

}} | }} | ||

MVS specific chip that does a bunch of unrelated things. | MVS specific chip that does a bunch of unrelated things. | ||

* [[S ROM]] 16bit address latch for [[SFIX]], same as S ROM portion of {{Chipname|NEO-273}} | * [[S ROM]] 16bit address latch for the [[SFIX ROM]], same as S ROM portion of {{Chipname|NEO-273}} | ||

* [[SM1]] /CS output when {{Chipname|Z80}} is reading from ROM and onboard ROMs are enabled | * [[SM1]] /CS output when {{Chipname|Z80}} is reading from ROM and onboard ROMs are enabled | ||

* {{Sig|ROMOE|ROMOE}} output for cartridge(s) [[PROG board]] | * {{Sig|ROMOE|ROMOE}} output for cartridge(s) [[PROG board]] | ||

| Line 17: | Line 17: | ||

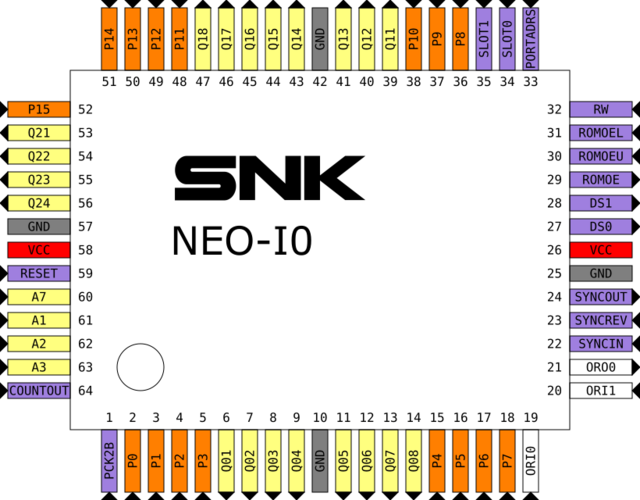

=Pinout= | =Pinout= | ||

{{Pinout|NEO-I0|640px}} | |||

*A1~A3,A7: {{Chipname|68k}} address bus | |||

* | *P0~P15: [[P bus]] | ||

*P0~P15: [[ | *Q01~Q18: [[SFIX ROM]] address lines | ||

*Q01~Q18: [[SFIX]] | |||

*SM1CS(ORO0): [[SM1]] ROM chip select, made from SYSTEM(ORI0) OR SDROM(ORI1) | *SM1CS(ORO0): [[SM1]] ROM chip select, made from SYSTEM(ORI0) OR SDROM(ORI1) | ||

*SYNCOUT = SYNCIN XOR SYNCREV (SYNCREV always tied to ground ?) | *SYNCOUT = SYNCIN XOR SYNCREV (SYNCREV always tied to ground ?) | ||

| Line 32: | Line 28: | ||

*Q23, Q24: LOCK1, LOCK2 | *Q23, Q24: LOCK1, LOCK2 | ||

*DS0, DS1: Data select for 2-slot systems made from SLOT0, SLOT1, PORTADRS and ROMOE, goes to a {{Chipname|NEO-G0}} | *DS0, DS1: Data select for 2-slot systems made from SLOT0, SLOT1, PORTADRS and ROMOE, goes to a {{Chipname|NEO-G0}} | ||

* | *COUNTOUT: Address decode from {{Chipname|NEO-F0}} | ||

[[Category:Chips]] | [[Category:Chips]] | ||

Latest revision as of 11:47, 18 November 2018

| |

| Package | QFP64R |

| Manufacturer | |

| First use | 1990 ? |

| Used on | MV2B MV1-1 ... |

MVS specific chip that does a bunch of unrelated things.

- S ROM 16bit address latch for the SFIX ROM, same as S ROM portion of NEO-273

- SM1 /CS output when Z80 is reading from ROM and onboard ROMs are enabled

- ROMOE output for cartridge(s) PROG board

- Video sync inversion (or not) to JAMMA connector

- Coin counter and coin lockout outputs

Pinout

- A1~A3,A7: 68k address bus

- P0~P15: P bus

- Q01~Q18: SFIX ROM address lines

- SM1CS(ORO0): SM1 ROM chip select, made from SYSTEM(ORI0) OR SDROM(ORI1)

- SYNCOUT = SYNCIN XOR SYNCREV (SYNCREV always tied to ground ?)

- Q21, Q22: METER1, METER2

- Q23, Q24: LOCK1, LOCK2

- DS0, DS1: Data select for 2-slot systems made from SLOT0, SLOT1, PORTADRS and ROMOE, goes to a NEO-G0

- COUNTOUT: Address decode from NEO-F0