PRO-CT0

| |

| Package | SDIP64 |

| Manufacturer | |

| First use | 1990 ? |

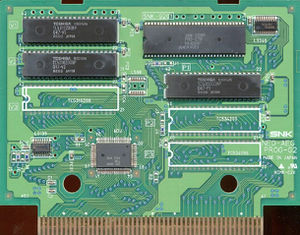

| Used on | MV4 Cartridges... |

PRO-CT0 (also known as SNK-9201 and ALPHA-8921) is an early gate array chip which serializes sprite graphics in AES cartridges and MVS boards. It was later replaced by NEO-ZMC2 and then NEO-CMC.

It was also used as a challenge-response "security" device in Super Sidekicks and Fatal Fury 2 cartridges.

ALPHA-8921 is the original chip name, from when Alpha Denshi were using it on their Alpha68k system.

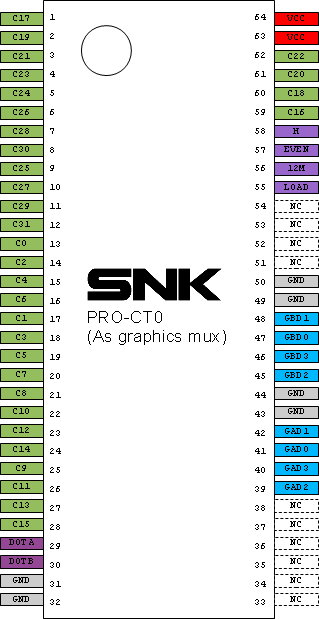

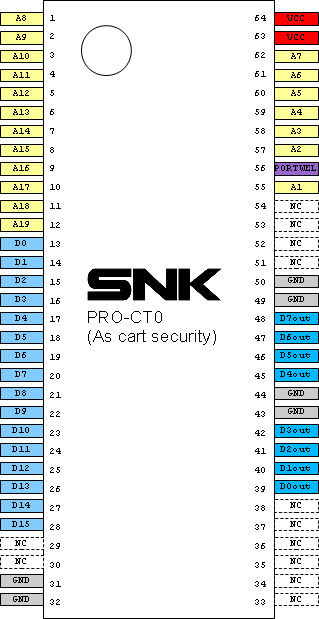

Pinouts

| Sprite graphics serializer | Security device |

|---|---|

|

|

| Info by User:Kyuusaku |

the 68k bus when /PORTOEL is low ($200000-$2FFFFF odd byte read). |

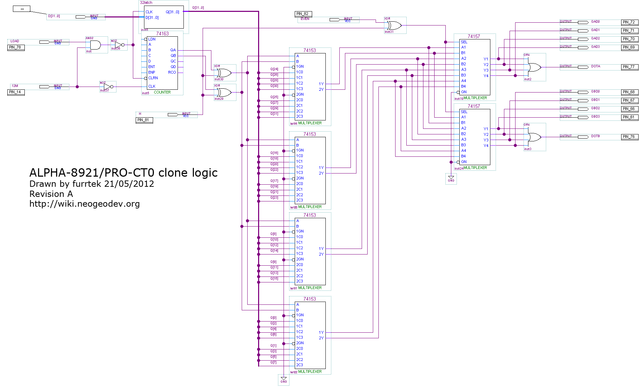

Internal logic

Kyuusaku's Verilog definition: File:Ct0.zip

furrtek's version:

Normal use: graphics serializer

See NEO-ZMC2.

Derivate use: security device

As a security device, the chip is only found on PROG-G2 boards for Fatal Fury 2 and Super Sidekicks. It was SNK's first attempt at copy-protecting NeoGeo games. The point was to make the game check for the presence of the chip, taking advantage of its relatively hard to guess logic.

The game programs expect the chip to reply with specific data depending on the values written to it. If the values don't match, then the game assumes it's a copy and silently sets a flag which triggers deliberate bugs during gameplay (see game pages for details).

The chip is tied to the 68k address and data bus, it reacts to word writes and replies on odd addresses in the $200000-$2FFFFF address range. Games use several unnecessary complicated bogus addresses in that range to make things look more complicated than they are.

Input

Address bus mapping:

| A19 | A18 | A17 | A16 | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | /PORTWEL | A1 |

| C31 | C29 | C27 | C25 | C30 | C28 | C26 | C24 | C23 | C21 | C19 | C17 | C22 | C20 | C18 | C16 | H | EVEN | 12M | LOAD |

Data bus mapping:

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| C15 | C13 | C11 | C9 | C14 | C12 | C10 | C8 | C7 | C5 | C3 | C1 | C6 | C4 | C2 | C0 |

Output

Data bus mapping:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| GBD1 | GBD0 | GBD3 | GBD2 | GAD1 | GAD0 | GAD3 | GAD2 |