YM2610 bus timing: Difference between revisions

Jump to navigation

Jump to search

(Created page with "800px == ADPCM-A ROM access == The access to the V ROMs are done sequentialy (in the channels order ?). A 666kHz clock is derived from the 8MHz ...") |

m (→Cycle relation) |

||

| (One intermediate revision by the same user not shown) | |||

| Line 1: | Line 1: | ||

[[File: | ==ADPCM-A bus== | ||

[[File:Adpcm-a_timing.png]] | |||

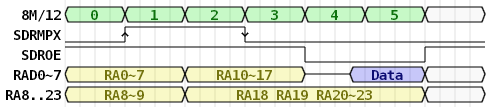

Access to the [[ADPCM]]-A [[V ROM|ROMs]] for each channel is done sequentialy (in the channels order ?). A ~667kHz clock is derived from the {{Chipname|YM2610}}'s 8MHz [[clock]] by dividing it by 12. | |||

* | * Period 0: The address LSBs are set | ||

* | * Period 1: SDRMPX goes high | ||

* | * Period 2: The address MSBs are set | ||

* Period 3: SDRMPX goes low | |||

* | * Period 4: SDROE goes low, RAD0~7 becomes hi-z | ||

* | * Period 5: ROM outputs data (when is it latched ?) | ||

* | |||

Each period is 1.5us, a complete read cycle is 6 * 1.5 = 9us. | |||

== ADPCM-B | ==ADPCM-B bus== | ||

[[File:Adpcm-b_timing.png]] | |||

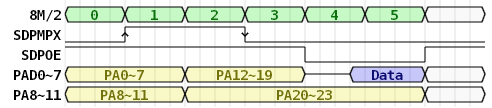

The access to the ADPCM-B ROMs is done synchronously with a 4MHz clock, derived from the 8MHz clock. | |||

* Period 0: The address LSBs are set | |||

* Period 1: SDPMPX goes high | |||

* Period 2: The address MSBs are set | |||

* Period 3: SDPMPX goes low | |||

* Period 4: SDPOE goes low, PAD0~7 becomes hi-z | |||

* Period 5: ROM outputs data (when is it latched ?) | |||

Each period is 250ns, each complete read cycle is 6 * 250 = 1.5us. Reads can happen every 2 ADPCM-A read at most (gives a 55.5kHz samplerate). | |||

==Cycle relation== | |||

{{Sig|SDROE|SDROE}} and {{Sig|SDPOE|SDPOE}} go low at the same time. | |||

[[Category:Audio system]] | [[Category:Audio system]] | ||

Latest revision as of 17:30, 12 November 2016

ADPCM-A bus

Access to the ADPCM-A ROMs for each channel is done sequentialy (in the channels order ?). A ~667kHz clock is derived from the YM2610's 8MHz clock by dividing it by 12.

- Period 0: The address LSBs are set

- Period 1: SDRMPX goes high

- Period 2: The address MSBs are set

- Period 3: SDRMPX goes low

- Period 4: SDROE goes low, RAD0~7 becomes hi-z

- Period 5: ROM outputs data (when is it latched ?)

Each period is 1.5us, a complete read cycle is 6 * 1.5 = 9us.

ADPCM-B bus

The access to the ADPCM-B ROMs is done synchronously with a 4MHz clock, derived from the 8MHz clock.

- Period 0: The address LSBs are set

- Period 1: SDPMPX goes high

- Period 2: The address MSBs are set

- Period 3: SDPMPX goes low

- Period 4: SDPOE goes low, PAD0~7 becomes hi-z

- Period 5: ROM outputs data (when is it latched ?)

Each period is 250ns, each complete read cycle is 6 * 250 = 1.5us. Reads can happen every 2 ADPCM-A read at most (gives a 55.5kHz samplerate).