MV1A: Difference between revisions

Jump to navigation

Jump to search

mNo edit summary |

(HC32 connections) |

||

| (4 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

==Description== | ==Description== | ||

A strangely designed MVS board which uses some chips found in the NeoGeo CD. Maybe allowed SNK to cut costs by using chips for both systems. | |||

{{SlotInfo | {{SlotInfo | ||

| Line 12: | Line 14: | ||

}} | }} | ||

==PALs== | |||

See [[MV1A PALs]]. | |||

==Scans== | ==Scans== | ||

| Line 17: | Line 22: | ||

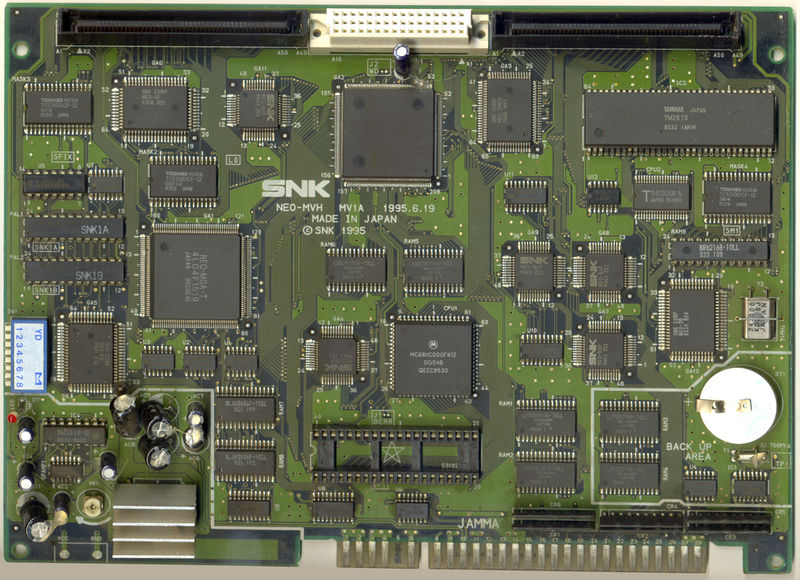

===Main Board=== | ===Main Board=== | ||

[[File:NEO-MVH MV1A Front. | [[File:NEO-MVH MV1A Front.jpg|800px|thumb|center|Main Board Front]] | ||

{{Chipname|NEO-BUF}} list: | |||

*GA4: 68k bidirectional palette access | |||

*GA7: Read P1 and P2 inputs | |||

*GA8: Only half used, read REG_STATUS_B | |||

*GA9: 68k/Z80 communication | |||

*GA11: 68k data bus bidirectional buffer | |||

Others: | |||

*U10: 68k to Z80 latch, clear = SDZ80CLR (NEO-D0 44), clock = SDW (SNK1A 22, NEO-D0 33) | |||

*U11: Z80 to 68k latch, no clear, clock = SDZ80W (NEO-D0 43) | |||

*U3: | |||

**3(RAM4 22) = SNK1B-4 OR MGA-51 | |||

**6(RAM3 22) = SNK1B-4 OR MGA-53 | |||

**8(U4 1) = SNK1B-4 OR MGA-52 | |||

**11(U4 4) = SNK1B-4 OR MGA-54 | |||

*U2: | |||

**3(Cart) = ROMOEL OR MGA-51 | |||

**6(Cart) = ROMOEL OR MGA-53 | |||

**8(Cart) = ROMOEL OR MGA-52 | |||

**11(Cart) = ROMOEL OR MGA-54 | |||

*U3: | |||

**3(Cart) = ROMOEU OR MGA-51 | |||

**6(Cart) = ROMOEU OR MGA-53 | |||

**8(Cart) = ROMOEU OR MGA-55 | |||

**11(Cart) = ROMOEU OR MGA-72 | |||

[[File:NEO-MVH MV1A Back. | [[File:NEO-MVH MV1A Back.jpg|800px|thumb|center|Main Board Back]] | ||

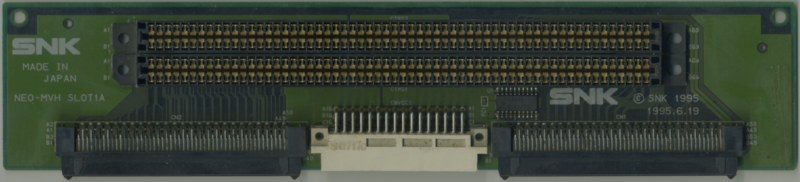

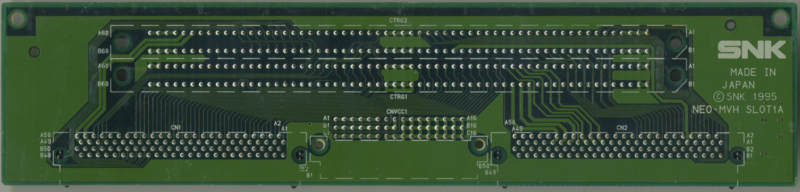

===Slot Board=== | ===Slot Board=== | ||

Latest revision as of 13:37, 13 May 2018

Description

A strangely designed MVS board which uses some chips found in the NeoGeo CD. Maybe allowed SNK to cut costs by using chips for both systems.

| Specification | |

| Year | Circa 1995 |

| Number of slots | 1 |

| System ROM | Socketed |

| Cart orientation | horizontal |

| Memory Card support | no |

| Joystick support | no |

| Stereo output | no |

| Headphone output | no |

PALs

See MV1A PALs.

Scans

Main Board

NEO-BUF list:

- GA4: 68k bidirectional palette access

- GA7: Read P1 and P2 inputs

- GA8: Only half used, read REG_STATUS_B

- GA9: 68k/Z80 communication

- GA11: 68k data bus bidirectional buffer

Others:

- U10: 68k to Z80 latch, clear = SDZ80CLR (NEO-D0 44), clock = SDW (SNK1A 22, NEO-D0 33)

- U11: Z80 to 68k latch, no clear, clock = SDZ80W (NEO-D0 43)

- U3:

- 3(RAM4 22) = SNK1B-4 OR MGA-51

- 6(RAM3 22) = SNK1B-4 OR MGA-53

- 8(U4 1) = SNK1B-4 OR MGA-52

- 11(U4 4) = SNK1B-4 OR MGA-54

- U2:

- 3(Cart) = ROMOEL OR MGA-51

- 6(Cart) = ROMOEL OR MGA-53

- 8(Cart) = ROMOEL OR MGA-52

- 11(Cart) = ROMOEL OR MGA-54

- U3:

- 3(Cart) = ROMOEU OR MGA-51

- 6(Cart) = ROMOEU OR MGA-53

- 8(Cart) = ROMOEU OR MGA-55

- 11(Cart) = ROMOEU OR MGA-72

Slot Board