L0 ROM: Difference between revisions

mNo edit summary |

mNo edit summary |

||

| (8 intermediate revisions by 4 users not shown) | |||

| Line 1: | Line 1: | ||

[[File:aes_lo.jpg|right|thumb|Toshiba LO ROM chip taken from an AES system.]] | [[File:aes_lo.jpg|right|thumb|Toshiba LO ROM chip taken from an AES system.]] | ||

[[File:cd2_lo.jpg|right|thumb|LO ROM chip found on a CDM3-2 board.]] | [[File:cd2_lo.jpg|right|thumb|LO ROM chip found on a CDM3-2 board.]] | ||

The L0 ROM is a 64KiB (sometimes 128KiB with A16 tied to ground) ROM chip found in every NeoGeo systems as a stand alone chip or integrated in another [[NEO-GRZ|chip]], which contains byte values used by {{Chipname|LSPC}} to shrink [[sprites]] '''vertically'''. | |||

The dump is called 000-lo.lo in [[system ROM]] sets. | |||

=Hash= | |||

* CRC32: 5A86CFF2 | |||

* SHA-1: 5992277DEBADEB64D1C1C64B0A92D9293EAF7E4A | |||

=Data format= | |||

The data | The data is made of 256 tables of 256 bytes, each table corresponding to a vertical shrinking value for sprites. | ||

For the first 256 lines ( | For the first 256 lines (top half of a full sprite), the index in the table is the line number of the sprite currently being drawn (scanline - Y position). | ||

Each byte is used as 2 nibbles: | Each byte entry in the table is used as 2 nibbles: | ||

*The upper nibble is the tile number index to read in the tilemap | *The upper nibble is the tile number index to read in the tilemap in [[VRAM]] SCB1 (0 to 15). | ||

*The lower nibble is the line number of that tile to fetch in the [[C ROM]]s. | *The lower nibble is the line number of that tile to fetch in the [[C ROM]]s. | ||

For the last 256 lines ( | For the last 256 lines (bottom half of a full sprite), the index in the table is complemented: the table is read backwards. | ||

*The upper nibble is the tile number index XOR $1F to read in the tilemap in VRAM SCB1 (16 to 31). | |||

*The upper nibble is the tile number index XOR $1F to read in the tilemap | |||

*The lower nibble is the line number XOR $F of that tile to fetch in the C ROMs. | *The lower nibble is the line number XOR $F of that tile to fetch in the C ROMs. | ||

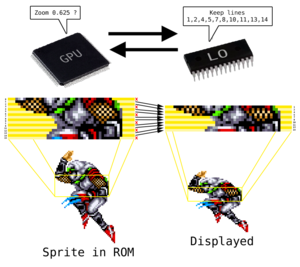

==Example of GPU processing== | ==Example of GPU processing== | ||

[[File:Ngscaling.png|right|thumb]] | |||

(Maybe place this part in the | (Maybe place this part in the LSPC page ?) | ||

Sprite with Y zoom value = $1B and tile height = 2 (32 pixels). | Sprite with Y zoom value = $1B and tile height = 2 (32 pixels). | ||

{|class=wikitable | |||

!Sprite line # | |||

!L0 address | |||

... | !L0 data | ||

!Tilemap index | |||

!Tile line used | |||

|- | |||

|0||$1B00||$00||0||0 | |||

... | |- | ||

|1||$1B01||$08||0||8 | |||

|- | |||

|2||$1B02||$10||1||0 | |||

|- | |||

|colspan=5|... | |||

|- | |||

|26||$1B1A||$E8||14||8 | |||

|- | |||

|27||$1B1B||$F8||15||8 | |||

|- | |||

|28||$1B1C||$FF||15||15 | |||

|- | |||

|29||$1B1D||$FF||15||15 | |||

|- | |||

|colspan=5|... | |||

|} | |||

==Datasheet== | ==Datasheet== | ||

There are 2 stand alone chip versions used depending on the NeoGeo system, the SOP32 TC531001 and the DIP28 TC531000. | |||

Official TC531001 datasheet: [[http://www.alldatasheet.com/datasheet-pdf/pdf/115078/TOSHIBA/TC531001.html]] | Official TC531001 datasheet: [[http://www.alldatasheet.com/datasheet-pdf/pdf/115078/TOSHIBA/TC531001.html]] | ||

Official TC531000 datasheet: [[https://www.digchip.com/datasheets/parts/datasheet/710/TC531000CP-pdf.php]] | |||

[[Category:Chips]] | [[Category:Chips]] | ||

Latest revision as of 21:37, 21 May 2020

The L0 ROM is a 64KiB (sometimes 128KiB with A16 tied to ground) ROM chip found in every NeoGeo systems as a stand alone chip or integrated in another chip, which contains byte values used by LSPC to shrink sprites vertically.

The dump is called 000-lo.lo in system ROM sets.

Hash

- CRC32: 5A86CFF2

- SHA-1: 5992277DEBADEB64D1C1C64B0A92D9293EAF7E4A

Data format

The data is made of 256 tables of 256 bytes, each table corresponding to a vertical shrinking value for sprites.

For the first 256 lines (top half of a full sprite), the index in the table is the line number of the sprite currently being drawn (scanline - Y position).

Each byte entry in the table is used as 2 nibbles:

- The upper nibble is the tile number index to read in the tilemap in VRAM SCB1 (0 to 15).

- The lower nibble is the line number of that tile to fetch in the C ROMs.

For the last 256 lines (bottom half of a full sprite), the index in the table is complemented: the table is read backwards.

- The upper nibble is the tile number index XOR $1F to read in the tilemap in VRAM SCB1 (16 to 31).

- The lower nibble is the line number XOR $F of that tile to fetch in the C ROMs.

Example of GPU processing

(Maybe place this part in the LSPC page ?)

Sprite with Y zoom value = $1B and tile height = 2 (32 pixels).

| Sprite line # | L0 address | L0 data | Tilemap index | Tile line used |

|---|---|---|---|---|

| 0 | $1B00 | $00 | 0 | 0 |

| 1 | $1B01 | $08 | 0 | 8 |

| 2 | $1B02 | $10 | 1 | 0 |

| ... | ||||

| 26 | $1B1A | $E8 | 14 | 8 |

| 27 | $1B1B | $F8 | 15 | 8 |

| 28 | $1B1C | $FF | 15 | 15 |

| 29 | $1B1D | $FF | 15 | 15 |

| ... | ||||

Datasheet

There are 2 stand alone chip versions used depending on the NeoGeo system, the SOP32 TC531001 and the DIP28 TC531000.

Official TC531001 datasheet: [[1]]

Official TC531000 datasheet: [[2]]