NEO-ZMC2: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

No edit summary |

||

| (19 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

{{ChipInfo | |||

|picture=mvs_zmc2.jpg | |||

|pkg=QFP80R | |||

|manu=fujitsu | |||

|date=1990 | |||

|gates= | |||

|used_on={{PCB|MV1FZS}} [[Cartridges]]... | |||

}} | |||

{{Chipname|NEO-ZMC}} and {{Chipname|PRO-CT0}} in one package. | |||

Can address up to 4MiB of [[M1 ROM]]. | |||

Found in second revision [[MVS hardware|MVS]] boards (for the PRO-CT0 logic only), and AES cartridges. | |||

=Pinout= | |||

* | {{Pinout|NEO-ZMC2|640px}} | ||

*MA11~ | |||

*12M: 12MHz clock ( | NEO-ZMC part: | ||

*GAD0~GAD3: Pixel A color | *SDA0,SDA1,SDA8~SDA15: [[Z80]] address bus | ||

*GBD0~GBD3: Pixel B color | *MA11~MA21: M ROM address outputs | ||

PRO-CT0 part, inputs: | |||

*12M: 12MHz clock, outputs next pixel on falling edge. | |||

*C0~C31: C ROM data bus (2*16 bits). Gives all the pixel data needed for a 8 pixel line. | |||

*H: When high, reverse bit order of pixels shifted out (used for [[sprites]] horizontal flipping) | |||

*EVEN: Swap A/B pixels. | |||

*LOAD: Latch C ROM data on rising edge of 12M. | |||

Outputs: | |||

*DOTA: High when pixel A is opaque (color > 0) | |||

*DOTB: High when pixel B is opaque (color > 0) | |||

*GAD0~GAD3: Pixel A color index | |||

*GBD0~GBD3: Pixel B color index | |||

[[Category:Chips]] | [[Category:Chips]] | ||

Latest revision as of 18:38, 19 September 2025

| |

| Package | QFP80R |

| Manufacturer | |

| First use | 1990 |

| Used on | MV1FZS Cartridges... |

NEO-ZMC and PRO-CT0 in one package.

Can address up to 4MiB of M1 ROM.

Found in second revision MVS boards (for the PRO-CT0 logic only), and AES cartridges.

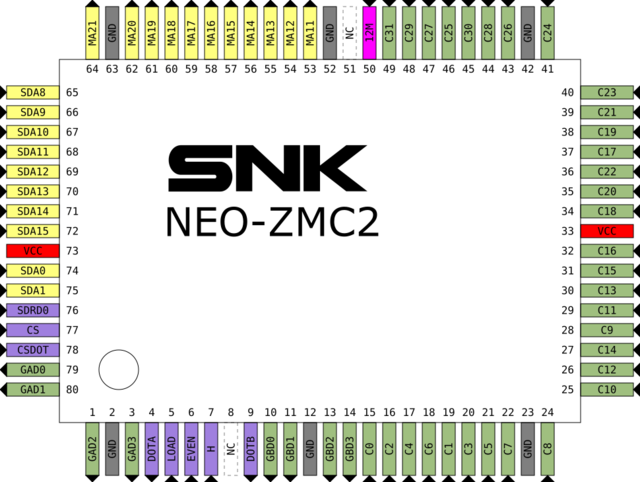

Pinout

NEO-ZMC part:

- SDA0,SDA1,SDA8~SDA15: Z80 address bus

- MA11~MA21: M ROM address outputs

PRO-CT0 part, inputs:

- 12M: 12MHz clock, outputs next pixel on falling edge.

- C0~C31: C ROM data bus (2*16 bits). Gives all the pixel data needed for a 8 pixel line.

- H: When high, reverse bit order of pixels shifted out (used for sprites horizontal flipping)

- EVEN: Swap A/B pixels.

- LOAD: Latch C ROM data on rising edge of 12M.

Outputs:

- DOTA: High when pixel A is opaque (color > 0)

- DOTB: High when pixel B is opaque (color > 0)

- GAD0~GAD3: Pixel A color index

- GBD0~GBD3: Pixel B color index