MV1A PALs: Difference between revisions

Jump to navigation

Jump to search

m (→SNK1B) |

m (→SNK1B) |

||

| (One intermediate revision by the same user not shown) | |||

| Line 9: | Line 9: | ||

JEDEC file: [[File:SNK1A.zip]] | JEDEC file: [[File:SNK1A.zip]] | ||

* /VPA = /i1 & A20 & A21 & A22I & A23I (Access Fxxxxx, interrupt ack cycle, signal 68k that we need an autovectored interrupt) | |||

* /WRAMCS = /i1 & A20 & /A21 & /A22I & /A23I (Access 1xxxxx, work RAM) | |||

* /o17 = /i1 & A20 & /A22I + /i1 & /A22I & A23I + /i1 & A22I & /A23I (Access x0x1 or 10xx (8xxxxx-Bxxxxx) or 01xx (4xxxxx-7xxxxx)) | |||

* /o18 = /i1 & A20 & /A21 & A22I & A23I (Access Dxxxxx, backup RAM) | |||

* /DIPRD0 = /i1 & /A17 & /A18 & /A19 & A20 & A21 & /A22I & /A23I & /MGA53 & MGA52 (Read 0011000x, must be 300000-31FFFF LDS) | |||

* /IN3 = /i1 & A17 & /A18 & /A19 & A20 & A21 & /A22I & /A23I & /MGA53 & MGA52 (Read 0011001x...) | |||

* /o21 = /i1 & A17 & /A18 & /A19 & A20 & A21 & /A22I & /A23I & /MGA51 & MGA52 (Read 0011001x...) | |||

* /SDW = /i1 & A17 & /A18 & /A19 & A20 & A21 & /A22I & /A23I & MGA51 & /MGA52 (Write 0011001x, must be 320000-33FFFE UDS) | |||

=SNK1B= | =SNK1B= | ||

| Line 16: | Line 25: | ||

JEDEC file: [[File:SNK1B.zip]] | JEDEC file: [[File:SNK1B.zip]] | ||

* o17 = /i5 & rf21 + /i5 & i11 + /i6 & rf21 & i23 + /i6 & i14 & rf22 + /i6 & i14 & i23 + /i2 & /i6 & /i14 & /i23 | |||

* DTACK = i3 & i7 & i8 & i9 & i10 & /o17 & /rf21 + i3 & i4 & i7 & i8 & i9 & i10 & /o17 | |||

* /rf20 = i4 & i5 & i6 | |||

* /rf21 = i4 & i5 & i6 + /rf20 | |||

* /rf22 = /rf21 + i4 & i5 & i6 | |||

[[Category:Chips]] | [[Category:Chips]] | ||

[[Category:Repairs]] | [[Category:Repairs]] | ||

Latest revision as of 23:26, 5 October 2023

The MV1A MVS boards have two [PAL] PAL20V8H-15 chips which are used to provide some of NEO-C1's functions. If any of them fails, the board certainly won't start up.

They can be replaced with new or working chips programmed with the following JEDEC files:

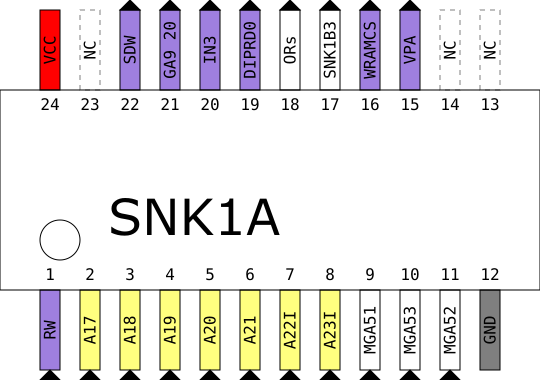

SNK1A

Does some address decoding. Pin 1 might be AS instead of RW.

JEDEC file: File:SNK1A.zip

- /VPA = /i1 & A20 & A21 & A22I & A23I (Access Fxxxxx, interrupt ack cycle, signal 68k that we need an autovectored interrupt)

- /WRAMCS = /i1 & A20 & /A21 & /A22I & /A23I (Access 1xxxxx, work RAM)

- /o17 = /i1 & A20 & /A22I + /i1 & /A22I & A23I + /i1 & A22I & /A23I (Access x0x1 or 10xx (8xxxxx-Bxxxxx) or 01xx (4xxxxx-7xxxxx))

- /o18 = /i1 & A20 & /A21 & A22I & A23I (Access Dxxxxx, backup RAM)

- /DIPRD0 = /i1 & /A17 & /A18 & /A19 & A20 & A21 & /A22I & /A23I & /MGA53 & MGA52 (Read 0011000x, must be 300000-31FFFF LDS)

- /IN3 = /i1 & A17 & /A18 & /A19 & A20 & A21 & /A22I & /A23I & /MGA53 & MGA52 (Read 0011001x...)

- /o21 = /i1 & A17 & /A18 & /A19 & A20 & A21 & /A22I & /A23I & /MGA51 & MGA52 (Read 0011001x...)

- /SDW = /i1 & A17 & /A18 & /A19 & A20 & A21 & /A22I & /A23I & MGA51 & /MGA52 (Write 0011001x, must be 320000-33FFFE UDS)

SNK1B

Generates the DTACK signal.

JEDEC file: File:SNK1B.zip

- o17 = /i5 & rf21 + /i5 & i11 + /i6 & rf21 & i23 + /i6 & i14 & rf22 + /i6 & i14 & i23 + /i2 & /i6 & /i14 & /i23

- DTACK = i3 & i7 & i8 & i9 & i10 & /o17 & /rf21 + i3 & i4 & i7 & i8 & i9 & i10 & /o17

- /rf20 = i4 & i5 & i6

- /rf21 = i4 & i5 & i6 + /rf20

- /rf22 = /rf21 + i4 & i5 & i6