Graphic glitches: Difference between revisions

m (→C ROM data) |

mNo edit summary |

||

| Line 2: | Line 2: | ||

todo: maybe add more detail, get rest of pics/descriptions up | todo: maybe add more detail, get rest of pics/descriptions up | ||

Glitches which: | |||

*Produce the same color pixel in 2x2 pixel blocks (dotted pattern) | |||

*Horizontally distort or misplace the sprites | |||

Are caused by bad connections between video chips (LSPC/B1...), not between the console and the cart. | |||

=Color problems= | |||

See palette RAM, DAC, DAC latches, palette address output from B1 or 68k address input to B1 for palette R/W... | |||

=C ROM= | =C ROM= | ||

Revision as of 06:54, 1 March 2014

This is supposed to be a repair guide that doesn't need much technical knowledge on the GFX hardware to understand. Only cart systems are covered here. Pics are provided for all glitches described and can be used to compare glitches that show up on faulty hardware for help in repairs.

todo: maybe add more detail, get rest of pics/descriptions up

Glitches which:

- Produce the same color pixel in 2x2 pixel blocks (dotted pattern)

- Horizontally distort or misplace the sprites

Are caused by bad connections between video chips (LSPC/B1...), not between the console and the cart.

Color problems

See palette RAM, DAC, DAC latches, palette address output from B1 or 68k address input to B1 for palette R/W...

C ROM

All sprites come from the C ROMs. Most graphics on screen are sprites as the Neo has no dedicated scrolling background layers like other systems. If it moves, scales or appears to be part of a background then assume it's a sprite.

C ROM address

C ROM address lines follow this path:

- LSPC2/LSPC-A0 to CHA slot (on multislots it will go through some buffers in between, NEO-257s or others)

- CHA slot to 74273 or similar(on oldest games)/NEO-273(on most games)/NEO-CMC(on newest games)

- 273/CMC to C ROM address lines

See pinouts for the slot pin numbers of the P0~23/CA4 signals listed in the table.

The two kind of glitches caused by the first 5 address lines and the upper ones is because of the way the sprites are drawn.

Lower address lines

A stuck lower address line for C ROMs causes certain patterns with display glitches. The graphics appear to be selected correctly but are glitched in various ways. A bad trace in the path of pins listed in the table can cause the glitch shown in the sample pic.

| Sample | Address | LSPC2-A2 out | LSPC-A0 out | NEO‑273 in | NEO‑273 out | C ROMs in | Notes |

|---|---|---|---|---|---|---|---|

| A0 | P16(134) | P16(98) | P16(57) | C_A0(64) | A0(10) | 1 row of pixels mirrored. Sprites appear "pixelated" as if it's lower res. | |

| A1 | P17(135) | P17(102) | P17(59) | C_A1(1) | A1(9) | Sets of 2 rows are mirrored. | |

| A2 | P18(136) | P18(103) | P18(25) | C_A2(32) | A2(8) | Sets of 4 rows are mirrored. | |

| A3 | P19(137) | P19(104) | P19(27) | C_A3(33) | A3(7) | Sets of 8 rows are mirrored. | |

| A4 | CA4(102) | CA4(125) | N/A | N/A | A4(6) | Sets of 8 columns are mirrored. Note NEO-273 isn't used and CA4 on CHA connector goes straight to C ROM A4. |

Higher address lines

Higher address lines can cause the 16x16 blocks of sprite graphics to appear without glitches but in completely wrong places. C ROM address A5 upwards can cause this. The patterns aren't obvious like they are for lower address lines so it's not as easy to diagnose. The sample pic to the right shows an example. Graphics from different stages, characters etc. can show up correctly but are misplaced.

C ROM data

Jailbars which are not forcibly every other pixel (this would indicate S ROM data bus problem).

S ROM

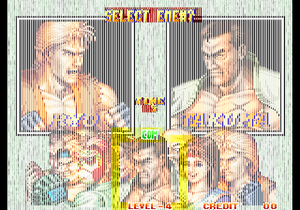

Graphics from the S ROM are used for stationary life bars, credit counters, on screen text and other graphics that don't need to move around. In the reference image, S ROM graphics are used for:

- "SELECT ENEMY"

- "TIME" and "5"

- "COM"

- "LEVEL-4" and "CREDIT 00"

They can't scroll or scale and they always appear "on top" of all sprites. This can cause S ROM issues to completely cover the screen while the opposite isn't true.

S ROM address

S ROM address lines follow the same path as C ROM address lines. 16 lines are shared with sprites and a single bad trace can affect both depending on what part of the path is affected. The NEO-273 (or whatever else is used) outputs separate S ROM/C ROM addresses from the shared address bus.

Lower address lines

Certain patterns appear for bad lower address lines like they do for C ROMs.

S ROM data

Data outputs from the S ROM go through FIXD0~FIXD7 on the cart slot. If any one of these traces is bad then it can cause glitches that cover the entire screen. A single bad output can cause every odd (or even) column of pixels on screen to be obscured. Sprites below can appear fine with half the screen covered up.