VRAM: Difference between revisions

mNo edit summary |

mNo edit summary |

||

| Line 3: | Line 3: | ||

[[File:Aes_cxk5814.jpg|thumb|One of two CXK5814 2KiB RAM chips used for the upper zone of the VRAM ($8000~$87FF) on a AES system]] | [[File:Aes_cxk5814.jpg|thumb|One of two CXK5814 2KiB RAM chips used for the upper zone of the VRAM ($8000~$87FF) on a AES system]] | ||

The NeoGeo has 68KiB (physically 64KiB + 4KiB) of VRAM organised as 16 bits words, which is used to store [[Sprites|sprite]] attributes | The NeoGeo has 68KiB (physically 64KiB + 4KiB, called lower and upper, or slow and fast) of VRAM organised as 16 bits words, which is used to store [[Sprites|sprite]] attributes, the [[fix layer]] tile map and sprite priority buffers for video rendering. Contrary to other systems, the VRAM here '''does not contain actual graphics'''. | ||

Acces to VRAM is done through 3 [[Memory mapped registers]] handled by the [[GPU]], it isn't mapped in the [[68k]] address space. Every VRAM address points to a word, not a byte. | |||

* | * {{Reg|REG_VRAMADDR ($3C0000)}} sets the VRAM address for the next read/write operation | ||

* | * {{Reg|REG_VRAMRW ($3C0002)}} is the data read or to write | ||

* | * {{Reg|REG_VRAMMOD ($3C0004)}} is the signed value added to the VRAM address after a write | ||

SNK specifies that the address register should be set directly instead of using auto-incrementation when changing between VRAM zones ($0000~$7FFF | SNK specifies that the address register should be set directly instead of using auto-incrementation when changing between VRAM zones ($0000~$7FFF to/from $8000~$FFFF). | ||

== Memory map == | == Memory map == | ||

| Line 27: | Line 27: | ||

|- | |- | ||

|$7000 | |$7000 | ||

|$74FF | |||

|[[Fix layer|Fix map]] | |||

|- | |||

|$7500 | |||

|$7FFF | |$7FFF | ||

|[[Fix | |[[Fix bankswiching|Extension]] | ||

|- | |- | ||

|$8000 | |$8000 | ||

| Line 61: | Line 65: | ||

After an address change, reads should be made after at least 16 cycles. | After an address change, reads should be made after at least 16 cycles. | ||

Note that these timings only affect the VRAM | Note that these timings only affect the VRAM access, and not the LSPC registers. | ||

[[Category:Video system]] | [[Category:Video system]] | ||

Revision as of 19:04, 24 December 2012

VRAM stand for Video RAM.

The NeoGeo has 68KiB (physically 64KiB + 4KiB, called lower and upper, or slow and fast) of VRAM organised as 16 bits words, which is used to store sprite attributes, the fix layer tile map and sprite priority buffers for video rendering. Contrary to other systems, the VRAM here does not contain actual graphics.

Acces to VRAM is done through 3 Memory mapped registers handled by the GPU, it isn't mapped in the 68k address space. Every VRAM address points to a word, not a byte.

- REG_VRAMADDR ($3C0000) sets the VRAM address for the next read/write operation

- REG_VRAMRW ($3C0002) is the data read or to write

- REG_VRAMMOD ($3C0004) is the signed value added to the VRAM address after a write

SNK specifies that the address register should be set directly instead of using auto-incrementation when changing between VRAM zones ($0000~$7FFF to/from $8000~$FFFF).

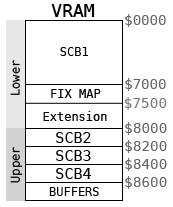

Memory map

| Start | End | Description |

| $0000 | $6FFF | SCB1 |

| $7000 | $74FF | Fix map |

| $7500 | $7FFF | Extension |

| $8000 | $81FF | SCB2 |

| $8200 | $83FF | SCB3 |

| $8400 | $85FF | SCB4 |

| $8600 | $867F | Sprite list for even scanlines |

| $8680 | $86FF | Sprite list for odd scanlines |

VRAM can be modified at any time, even during active display.

Timing considerations

After a write:

- Another write should be made after at least 12 cycles.

- An address change should be made after at least 16 cycles.

After an address change, reads should be made after at least 16 cycles.

Note that these timings only affect the VRAM access, and not the LSPC registers.