CD drive: Difference between revisions

Jump to navigation

Jump to search

mNo edit summary |

(Signal infos) |

||

| Line 6: | Line 6: | ||

It is made of: | It is made of: | ||

* A 4-bit | * A 4-bit maskROM MCU (Sony CXP5084), taking care of sequencing and communication (command execution and status report). | ||

* A DSP (CXD2500) to process analog data from the pickup | * A DSP (Sony CXD2500) to process analog data from the pickup. | ||

* A servo controler (CXA1372) to drive the pickup coils for tracking and focus | * A servo controler (Sony CXA1372) to drive the pickup coils for tracking and focus. | ||

* A spindle motor driver (Rohm BA6396) | * A spindle and sled motor driver (Rohm BA6396). | ||

==Communication== | ==Communication== | ||

Some say the protocol was | Some say the protocol was standard for the time, but clear information is hard to find. This was guessed from the [[system ROM]] disassembly and a logic analyzer. | ||

Connector pinout, directions are from CDD (CD Drive) to CDC (CD Controller): | |||

{| class="regdef" | |||

|'''Pin #''' | |||

|'''Name''' | |||

|'''Type''' | |||

|'''Direction''' | |||

|'''Description''' | |||

|- | |||

| 1 | |||

| CDCK | |||

| Clock | |||

| Output | |||

*12 SDATA | | Tells the CDC when to change HOCK | ||

|- | |||

| 2 | |||

| ? | |||

| ? | |||

| ? | |||

| High ? | |||

|- | |||

| 3 | |||

| /IRQ | |||

| Signal | |||

| Output | |||

| Asks the CDC for a data exchange (low pulse at ~64Hz) | |||

|- | |||

| 4 | |||

| ? | |||

| ? | |||

| ? | |||

| High ? | |||

|- | |||

| 5 | |||

| HOCK | |||

| Clock | |||

| Input | |||

| Tells the CDD data is ready on D0~3 | |||

|- | |||

| 6 | |||

| rowspan="4" | D0~3 | |||

| rowspan="4" | Data | |||

| rowspan="4" | Both | |||

| rowspan="4" | 4-bit data bus | |||

|- | |||

| 7 | |||

|- | |||

| 8 | |||

|- | |||

| 9 | |||

|- | |||

| 10 | |||

| ? | |||

| ? | |||

| ? | |||

| ? | |||

|- | |||

| 11 | |||

| BCLK? | |||

| Clock | |||

| Output | |||

| I2S bit clock, should be 44100 * 32 = 1.4112MHz | |||

|- | |||

| 12 | |||

| SDATA | |||

| Data | |||

| Output | |||

| I2S data | |||

|- | |||

| 13 | |||

| LRCK | |||

| Signal | |||

| Output | |||

| I2S word clock, should be 44100Hz. Audio L/R switch for the DAC. | |||

|- | |||

| 14 | |||

| MUTE? | |||

| Signal | |||

| Input | |||

| Put low to gate SDATA ? | |||

|- | |||

| 15 | |||

| GND | |||

| Power | |||

| - | |||

| Ground | |||

|- | |||

| 16 | |||

| 5V | |||

| Power | |||

| - | |||

| +5V for logic | |||

|- | |||

| 17 | |||

| 9V | |||

| Power | |||

| - | |||

| +9V for motors and coils | |||

|- | |||

| 18 | |||

| GND | |||

| Power | |||

| - | |||

| Ground | |||

|} | |||

Some signal has to be "D/M", an output which indicates if SDATA is audio or data. | Some signal has to be "D/M", an output which indicates if SDATA is audio or data. There's a /RESET somewhere also. | ||

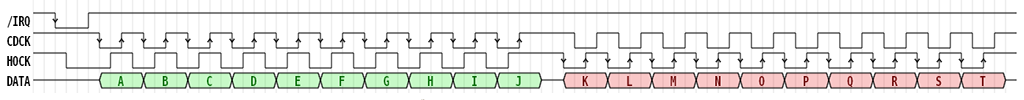

Done through [[NEO-MGA]] on a 4-bit bi-directional bus. | Done through [[NEO-MGA]] on a 4-bit bi-directional bus. | ||

[[File:Cdunit4bit.png]] | [[File:Cdunit4bit.png]] | ||

==Adjustments== | ==Adjustments== | ||

Revision as of 23:36, 1 June 2016

Or "CD drive". The part that fails before everything else in CD systems. Also see optical pickups.

The NeoGeo CD top-loading model drive was made by Sony. The CDZ one was made by Sharp ?

It is made of:

- A 4-bit maskROM MCU (Sony CXP5084), taking care of sequencing and communication (command execution and status report).

- A DSP (Sony CXD2500) to process analog data from the pickup.

- A servo controler (Sony CXA1372) to drive the pickup coils for tracking and focus.

- A spindle and sled motor driver (Rohm BA6396).

Communication

Some say the protocol was standard for the time, but clear information is hard to find. This was guessed from the system ROM disassembly and a logic analyzer.

Connector pinout, directions are from CDD (CD Drive) to CDC (CD Controller):

| Pin # | Name | Type | Direction | Description |

| 1 | CDCK | Clock | Output | Tells the CDC when to change HOCK |

| 2 | ? | ? | ? | High ? |

| 3 | /IRQ | Signal | Output | Asks the CDC for a data exchange (low pulse at ~64Hz) |

| 4 | ? | ? | ? | High ? |

| 5 | HOCK | Clock | Input | Tells the CDD data is ready on D0~3 |

| 6 | D0~3 | Data | Both | 4-bit data bus |

| 7 | ||||

| 8 | ||||

| 9 | ||||

| 10 | ? | ? | ? | ? |

| 11 | BCLK? | Clock | Output | I2S bit clock, should be 44100 * 32 = 1.4112MHz |

| 12 | SDATA | Data | Output | I2S data |

| 13 | LRCK | Signal | Output | I2S word clock, should be 44100Hz. Audio L/R switch for the DAC. |

| 14 | MUTE? | Signal | Input | Put low to gate SDATA ? |

| 15 | GND | Power | - | Ground |

| 16 | 5V | Power | - | +5V for logic |

| 17 | 9V | Power | - | +9V for motors and coils |

| 18 | GND | Power | - | Ground |

Some signal has to be "D/M", an output which indicates if SDATA is audio or data. There's a /RESET somewhere also.

Done through NEO-MGA on a 4-bit bi-directional bus.

Adjustments

To do !