Super MVS convertor II: Difference between revisions

Jump to navigation

Jump to search

(Created page with "<div align="center"> <gallery widths=400px perrow=2> File:SMC2_progtop.jpg|Prog board top File:SMC2_progbot.jpg|Prog board bottom File:SMC2_chatop.jpg|CHA board top File:SMC2_...") |

m (Added templates, removed dead link) |

||

| Line 10: | Line 10: | ||

[[File:Neocellks300.jpg|thumb]] | [[File:Neocellks300.jpg|thumb]] | ||

Uses a PAL18CV8 and two LS245 transceivers on the prog board. Two corresponding footprints for SIL pull-up resistors on the MVS side are left unpopulated. | Uses a PAL18CV8 and two LS245 transceivers for the [[68k]] data bus on the prog board. Two corresponding footprints for SIL pull-up resistors on the MVS side are left unpopulated. | ||

Unrouted signals: | Unrouted signals: | ||

* 4MB (MVS B34) | * {{Sig|4MB|4MB}} (MVS B34) | ||

* SLOTCS (MVS A42) | * {{Sig|SLOTCS|SLOTCS}} (MVS A42) | ||

Uses a | Uses a chip marked ''Neo Cell KS300 8436020333002 06-03'' to simulate {{Chipname|PRO-CT0}} logic. An RC circuit (potentiometer) is used to delay the {{Sig|EVEN|EVEN}} signal. | ||

The chip is actually a custom marked Altera MAX EPM240 CPLD. Boundary scan device ID replies BB085040 (EPM240 signature reversed) and the header on the back is for JTAG: | |||

{|class="wikitable" | {|class="wikitable" | ||

Latest revision as of 08:08, 10 January 2017

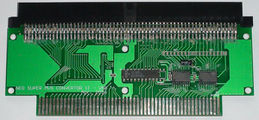

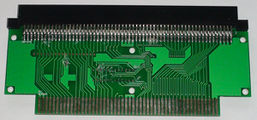

Uses a PAL18CV8 and two LS245 transceivers for the 68k data bus on the prog board. Two corresponding footprints for SIL pull-up resistors on the MVS side are left unpopulated.

Unrouted signals:

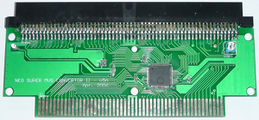

Uses a chip marked Neo Cell KS300 8436020333002 06-03 to simulate PRO-CT0 logic. An RC circuit (potentiometer) is used to delay the EVEN signal.

The chip is actually a custom marked Altera MAX EPM240 CPLD. Boundary scan device ID replies BB085040 (EPM240 signature reversed) and the header on the back is for JTAG:

| TMS | TDO | GND |

| TDI | TCK | 3.3V |