LC89515: Difference between revisions

(Registers and commands) |

|||

| (2 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

[[File:cd2_lc89515.jpg|right|thumb|Sanyo LC89515 chip found on a CDM3-2 board.]] | [[File:cd2_lc89515.jpg|right|thumb|Sanyo LC89515 chip found on a CDM3-2 board.]] | ||

CD- | Sanyo CD-ROM host and error correction chip, also known as RCHIP. Used to [[Loading files|load files]] in CD systems. It uses a 64KiB RAM buffer (2 32KiB RAM chips), which is able to store up to 27 CD-ROM sectors. | ||

DMA copy speed from buffer to [[DRAM]]s can go up to 2.3MiB/s (16.9344MHz / 7 ?) | |||

The NeoGeo CD does not use the C2 pointer error correction. | |||

Complete datasheet: [[ | The NeoGeo [[CDZ]] uses the {{Chipname|LC89513}}. | ||

=Datasheet= | |||

Complete datasheet: [[https://www.megadrive.org/elbarto/megacd/Official%20Sega%20CD%20Manual/LC8951/]] | |||

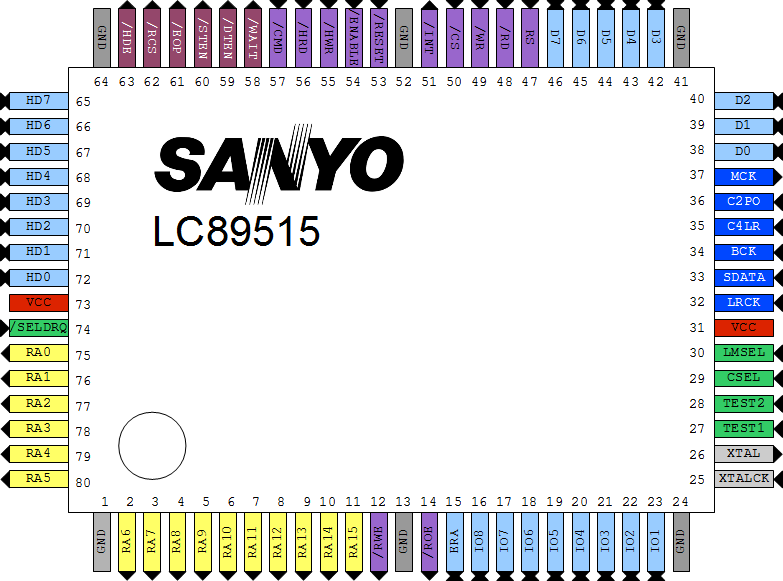

=Pinout= | |||

[[File:Lc89515.png]] | |||

=Registers= | |||

Registers access is done through {{Reg|$FF0101}} and {{Reg|$FF0103}}. | |||

Read and writes auto-increments the register address except from register #0. After register #15, the address loops back to #0. | |||

{|class="wikitable | |||

! ||colspan=2|Read||colspan=2|Write | |||

|- | |||

!#||Name||Definition||Name||Definition | |||

|- | |||

|0 | |||

|COMIN | |||

|Command FIFO input (unused in NeoGeo CD ?) | |||

|SBOUT | |||

|Status byte output (unused in NeoGeo CD ?) | |||

|- | |||

|1 | |||

|IFSTAT | |||

|{{8BitRegister|/CMDI|1|/DTEI|1|/DECI|1|1|1|/DTBSY|1|/STBSY|1|/DTEN|1|/STEN|1}} | |||

|IFCTRL | |||

|{{8BitRegister|CMDIEN|1|DTEIEN|1|DECIEN|1|/CMDBK|1|/DTWAI|1|/STWAI|1|/DOUTEN|1|/SOUTEN|1}} | |||

|- | |||

|2 | |||

|DBCL | |||

|colspan=3|Data byte counter 8 LSBs | |||

|- | |||

|3 | |||

|DBCH | |||

|{{8BitRegister|DTEI|4|Data byte counter 4 MSBs|4}} | |||

|DBCH | |||

|{{8BitRegister|-|4|Data byte counter 4 MSBs|4}} | |||

|- | |||

|4 | |||

|HEAD0 | |||

| | |||

{|class="wikitable | |||

|SHDREN=0||SHDREN=1 | |||

|- | |||

|Header minutes||Subheader file # | |||

|} | |||

|DACL | |||

|Data start address 8 LSBs | |||

|- | |||

|5 | |||

|HEAD1 | |||

| | |||

{|class="wikitable | |||

|SHDREN=0||SHDREN=1 | |||

|- | |||

|Header seconds||Subheader channel # | |||

|} | |||

|DACH | |||

|Data start address 8 MSBs | |||

|- | |||

|6 | |||

|HEAD2 | |||

| | |||

{|class="wikitable | |||

|SHDREN=0||SHDREN=1 | |||

|- | |||

|Header frames||Subheader submode # | |||

|} | |||

|DTTRG | |||

|Any write triggers a transfer start | |||

|- | |||

|7 | |||

|HEAD3 | |||

| | |||

{|class="wikitable | |||

|SHDREN=0||SHDREN=1 | |||

|- | |||

|Header mode (01)||Subheader coding info | |||

|} | |||

|DTACK | |||

|Any write acknowledges the transfer interrupt | |||

|- | |||

|8 | |||

|PTL | |||

|Last decoded sector address 8 LSBs | |||

|WAL | |||

|Pointer to start of data to be loaded 8 LSBs | |||

|- | |||

|9 | |||

|PTH | |||

|Last decoded sector address 8 MSBs | |||

|WAH | |||

|Pointer to start of data to be loaded 8 MSBs | |||

|- | |||

|10 | |||

|WAL | |||

|Pointer to start of data to be loaded 8 LSBs | |||

|CTRL0 | |||

|{{8BitRegister|DCEN|1|EDCRQ|1|E01RQ|1|AUTORQ|1|ERAMRQ|1|WRRQ|1|QRQ|1|PRQ|1}} | |||

|- | |||

|11 | |||

|WAH | |||

|Pointer to start of data to be loaded 8 MSBs | |||

|CTRL1 | |||

|{{8BitRegister|SYIEN|1|SYDEN|1|DSCREN|1|COWREN|1|MODRQ|1|FORMRQ|1|-|1|SHDREN|1}} | |||

|- | |||

|12 | |||

|STAT0 | |||

|{{8BitRegister|CRCOK|1|ILSYNC|1|NOSYNC|1|LBLK|1|WSHORT|1|SBLK|1|ERABLK|1|UCEBLK|1}} | |||

|PTL | |||

|Pointer to start of data to be decoded 8 MSBs | |||

|- | |||

|13 | |||

|STAT1 | |||

|{{8BitRegister|MINERA|1|SECERA|1|BLKERA|1|MODERA|1|SH0ERA|1|SH1ERA|1|SH2ERA|1|SH3ERA|1}} | |||

Error flags for HEAD0~HEAD3 | |||

|PTH | |||

|Pointer to start of data to be decoded 8 LSBs | |||

|- | |||

|14 | |||

|STAT2 | |||

|{{8BitRegister|-|4|MODE|1|FORM|1|-|2}} | |||

|Unused | |||

| | |||

|- | |||

|15 | |||

|STAT3 | |||

|{{8BitRegister|/VALST|1|WLONG|1|-|6}} | |||

|RESET | |||

| | |||

|} | |||

=Notes= | |||

If CD command FIFO is not empty, status FIFO[1] = 15 (busy ?). | |||

* Command 0: Nop ? | |||

* Command 1: | |||

<pre> | |||

CDEmuStop(); | |||

NeoCDAssyStatus = 0x0E; | |||

</pre> | |||

* Command 2: | |||

<pre> | |||

status FIFO[1]=command FIFO[3] | |||

</pre> | |||

** 0: Read Q subcode first 6 digits | |||

Data in FIFO[2~7] & FIFO[8] | |||

** 1: Read Q subcode next 6 digits | |||

Data in FIFO[2~7] & FIFO[8] | |||

** 2: Read Q subcode last 2 digits | |||

Data in FIFO[2~3] & FIFO[8] | |||

** 3: Read subcode TOC -2? | |||

Data in FIFO[2~7] | |||

** 4: Read subcode TOC -1? | |||

Data in FIFO[2~5] | |||

** 5: Read TOC from track in FIFO[4~5] | |||

Data in FIFO[2~7] & FIFO[8] | |||

<pre> | |||

// bit 3 of the 1st minutes digit indicates a data track | |||

if (TOCEntry[3] & 4) { | |||

NeoCDCommsStatusFIFO[6] |= 8; | |||

} | |||

</pre> | |||

** 6: Read Q subcode status ? | |||

Data in FIFO[8] only | |||

** 7: Clear FIFO ? | |||

FIFO[3] = 5 | |||

* 3: Switch mode according to reg. #10 bit 2 | |||

MSF set in FIFO[2~3]. Starts reading disc. | |||

* 4: Pasue | |||

* 5: | |||

<pre> | |||

NeoCDAssyStatus = 4; | |||

bNeoCDLoadSector = false; | |||

</pre> | |||

* 7: | |||

<pre> | |||

NeoCDAssyStatus = 1; | |||

bNeoCDLoadSector = true; | |||

</pre> | |||

[[Category:Chips]] | [[Category:Chips]] | ||

Latest revision as of 16:21, 10 February 2017

Sanyo CD-ROM host and error correction chip, also known as RCHIP. Used to load files in CD systems. It uses a 64KiB RAM buffer (2 32KiB RAM chips), which is able to store up to 27 CD-ROM sectors.

DMA copy speed from buffer to DRAMs can go up to 2.3MiB/s (16.9344MHz / 7 ?)

The NeoGeo CD does not use the C2 pointer error correction.

The NeoGeo CDZ uses the LC89513.

Datasheet

Complete datasheet: [[1]]

Pinout

Registers

Registers access is done through $FF0101 and $FF0103.

Read and writes auto-increments the register address except from register #0. After register #15, the address loops back to #0.

| Read | Write | |||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| # | Name | Definition | Name | Definition | ||||||||||||||||||||||||||||||||||||

| 0 | COMIN | Command FIFO input (unused in NeoGeo CD ?) | SBOUT | Status byte output (unused in NeoGeo CD ?) | ||||||||||||||||||||||||||||||||||||

| 1 | IFSTAT |

|

IFCTRL |

| ||||||||||||||||||||||||||||||||||||

| 2 | DBCL | Data byte counter 8 LSBs | ||||||||||||||||||||||||||||||||||||||

| 3 | DBCH |

|

DBCH |

| ||||||||||||||||||||||||||||||||||||

| 4 | HEAD0 |

|

DACL | Data start address 8 LSBs | ||||||||||||||||||||||||||||||||||||

| 5 | HEAD1 |

|

DACH | Data start address 8 MSBs | ||||||||||||||||||||||||||||||||||||

| 6 | HEAD2 |

|

DTTRG | Any write triggers a transfer start | ||||||||||||||||||||||||||||||||||||

| 7 | HEAD3 |

|

DTACK | Any write acknowledges the transfer interrupt | ||||||||||||||||||||||||||||||||||||

| 8 | PTL | Last decoded sector address 8 LSBs | WAL | Pointer to start of data to be loaded 8 LSBs | ||||||||||||||||||||||||||||||||||||

| 9 | PTH | Last decoded sector address 8 MSBs | WAH | Pointer to start of data to be loaded 8 MSBs | ||||||||||||||||||||||||||||||||||||

| 10 | WAL | Pointer to start of data to be loaded 8 LSBs | CTRL0 |

| ||||||||||||||||||||||||||||||||||||

| 11 | WAH | Pointer to start of data to be loaded 8 MSBs | CTRL1 |

| ||||||||||||||||||||||||||||||||||||

| 12 | STAT0 |

|

PTL | Pointer to start of data to be decoded 8 MSBs | ||||||||||||||||||||||||||||||||||||

| 13 | STAT1 |

Error flags for HEAD0~HEAD3 |

PTH | Pointer to start of data to be decoded 8 LSBs | ||||||||||||||||||||||||||||||||||||

| 14 | STAT2 |

|

Unused | |||||||||||||||||||||||||||||||||||||

| 15 | STAT3 |

|

RESET | |||||||||||||||||||||||||||||||||||||

Notes

If CD command FIFO is not empty, status FIFO[1] = 15 (busy ?).

- Command 0: Nop ?

- Command 1:

CDEmuStop(); NeoCDAssyStatus = 0x0E;

- Command 2:

status FIFO[1]=command FIFO[3]

- 0: Read Q subcode first 6 digits

Data in FIFO[2~7] & FIFO[8]

- 1: Read Q subcode next 6 digits

Data in FIFO[2~7] & FIFO[8]

- 2: Read Q subcode last 2 digits

Data in FIFO[2~3] & FIFO[8]

- 3: Read subcode TOC -2?

Data in FIFO[2~7]

- 4: Read subcode TOC -1?

Data in FIFO[2~5]

- 5: Read TOC from track in FIFO[4~5]

Data in FIFO[2~7] & FIFO[8]

// bit 3 of the 1st minutes digit indicates a data track

if (TOCEntry[3] & 4) {

NeoCDCommsStatusFIFO[6] |= 8;

}

- 6: Read Q subcode status ?

Data in FIFO[8] only

- 7: Clear FIFO ?

FIFO[3] = 5

- 3: Switch mode according to reg. #10 bit 2

MSF set in FIFO[2~3]. Starts reading disc.

- 4: Pasue

- 5:

NeoCDAssyStatus = 4; bNeoCDLoadSector = false;

- 7:

NeoCDAssyStatus = 1; bNeoCDLoadSector = true;