Reset: Difference between revisions

Jump to navigation

Jump to search

(Created page with "VCCON (MVS) or RST (AES reset button, PST518B) -> NEO-B1 -> RESET (rises slowly, open collector in B1 ?) -> LSPC -> RESETP. Notes: * VCCON/RST depends on power supply or use...") |

mNo edit summary |

||

| Line 10: | Line 10: | ||

RESET might be synchronized with a clock reaching B1 (1MB ? 6MB ?). | RESET might be synchronized with a clock reaching B1 (1MB ? 6MB ?). | ||

RESETP is triggered by the watchdog also (since it asserts RESET). | |||

[[Category:Base system]] | [[Category:Base system]] | ||

Revision as of 17:05, 14 June 2016

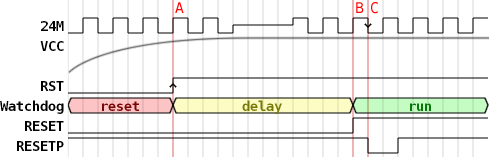

VCCON (MVS) or RST (AES reset button, PST518B) -> NEO-B1 -> RESET (rises slowly, open collector in B1 ?) -> LSPC -> RESETP.

Notes:

- VCCON/RST depends on power supply or user input (main reset signal)

- NEO-B1 ANDs it with the watchdog reset signal (internal), or simply resets the watchdog timer to force a watchdog reset as long as VCCON/RST is low ?

- LSPC generates RESETP, which is a 1mclk long negative pulse sync'd to mclk falling edge triggered when RESET rises (used to sync clocks in NEO-D0)

RESET might be synchronized with a clock reaching B1 (1MB ? 6MB ?).

RESETP is triggered by the watchdog also (since it asserts RESET).