161-in-1 Series 1

Relatively recent multicart with a software menu.

Programming

Infos by Razoola.

Games have their v-blank interrupt code patched to allow going back to the menu. The button press check is flawed: it assumes no memory card is present. If a memory card is present, the check will never pass and the menu won't appear.

Address 0x2FFFE0 (word) is used to communicate with the mcu for storage and retrieval of the game's software DIPs settings and the menu's current position.

Game selection seems to be done through a set of 3 registers (0x2FFF00, 0x2FFFF2, and 0x2FFFF6), where only the game number is written.

Boards

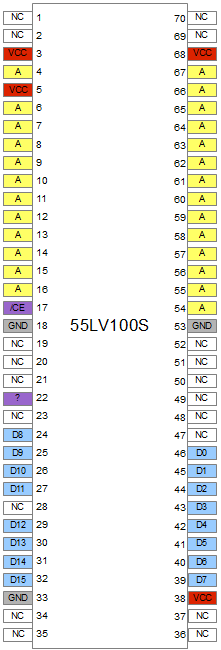

Uses a bunch of uncommon Fujitsu SSOP70 55LV100S 128MB flash chips, which some say were salvaged from other arcade machines.

- 3 for P (384MB)

- 5 for V (640MB)

- 16 for C (2GB)

- 1 for S

- 1 for M

PROG board

- UP1: EPM3256 CPLD for P ROM and mcu control. Full 68k address and data bus connected. Address bus for the P ROMs comes only from the CPLD. Connected to RESET, PORTWE, PORTOE, ROMOE, AS, RW. JTAG port is JP1.

- U3: Microcontroller (sanded-off PIC ?). 5V-powered, 8bit input bus (3.3V pullups in SIL array) and 8bit output bus to UP1. Not present on earlier multicarts of the same origin with less games. Programming port is J8.

CHA board

Another EPM3256 CPLD for the C, S and M ROMs. A smaller CPLD is used to replace NEO-ZMC.

Uses a daughterboard with 14 flash chips. Lots of unused footprints for additional chips.