CHA42G

Jump to navigation

Jump to search

Can handle 4 2MiB or 1MiB C ROMs with a special trick.

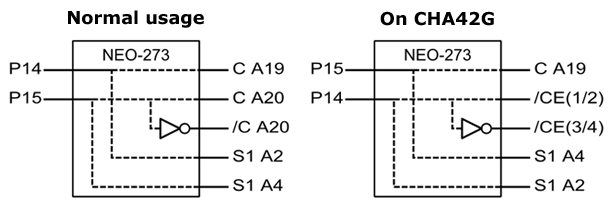

On this board, the P14, P15, S1 A2 and S1 A4 lines are reversed on NEO-273. These inversions cancel each other out for the M1 ROM, but the C ROMs A20 and A19 output are inverted.

This was done to benefit of the NEO-273's inverted A20 output on the A19 line instead to switch between pairs of 1MiB C ROMs without additionnal circuitry. However, this has the side-effect of mixing data up if 2MiB C ROMs are used:

For tiles to be used properly in 2MiB ROMs, data must be organized as follows:

- C1 = First 1MiB of C1 + First 1MiB of C3

- C2 = First 1MiB of C2 + First 1MiB of C4

- C3 = Second 1MiB of C1 + Second 1MiB of C3

- C4 = Second 1MiB of C2 + Second 1MiB of C4

In MAME, in the Fatal Fury 2 definition for example, the 4 2MiB C ROMs are loaded in a special order to sort them back out:

ROM_LOAD16_BYTE( "047-c1.c1", 0x000000, 0x100000... // First half of C1 loaded in even bytes of 0x000000~0x1FFFFE ROM_CONTINUE( 0x400000, 0x100000 ) // Second half of C1 loaded in even bytes of 0x400000~0x5FFFFE ROM_LOAD16_BYTE( "047-c2.c2", 0x000001, 0x100000... // First half of C2 loaded in odd bytes of 0x000001~0x1FFFFF ROM_CONTINUE( 0x400001, 0x100000 ) // Second half of C2 loaded in odd bytes of 0x400001~0x5FFFFF ROM_LOAD16_BYTE( "047-c3.c3", 0x200000, 0x100000... // First half of C3 loaded in even bytes of 0x200000~0x3FFFFE ROM_CONTINUE( 0x600000, 0x100000 ) // Second half of C3 loaded in even bytes of 0x600000~0x7FFFFE ROM_LOAD16_BYTE( "047-c4.c4", 0x200001, 0x100000... // First half of C4 loaded in odd bytes of 0x200001~0x3FFFFF ROM_CONTINUE( 0x600001, 0x100000 ) // Second half of C4 loaded in odd bytes of 0x600001~0x7FFFFF

- 0x000000~0x1FFFFF: First half of C1 and C2

- 0x200000~0x3FFFFF: First half of C3 and C4

- 0x400000~0x5FFFFF: Second half of C1 and C2

- 0x600000~0x7FFFFF: Second half of C3 and C4

Next revision: CHA42G-1.