PROGBK1: Difference between revisions

mNo edit summary |

m (V ROM 32MiB type) |

||

| (2 intermediate revisions by 2 users not shown) | |||

| Line 82: | Line 82: | ||

!Nothing | !Nothing | ||

|- | |- | ||

|A19/NC is /PORTADRS | |A19/NC is /PORTADRS (P1 is 16Mbit) | ||

|A19/NC is BANK0 ( | |A19/NC is BANK0 (because reasons?) | ||

|P1 is 8Mbit | |P1 is 8Mbit | ||

|} | |} | ||

| Line 108: | Line 108: | ||

[[File:Progbk1v.png]] | [[File:Progbk1v.png]] | ||

There is a maximum of 4 [[V ROM]]s which can be 8Mbit, 16Mbit or 32Mbit (27C800/27C160) for a maximum total size of 4 * 4MiB = 16MiB. | There is a maximum of 4 [[V ROM]]s which can be 8Mbit, 16Mbit or 32Mbit (27C800/27C160/27C322) for a maximum total size of 4 * 4MiB = 16MiB. | ||

A 4Mbit ROM can also be used, but only if there's one and only if it's in the last used slot. | A 4Mbit ROM can also be used, but only if there's one and only if it's in the last used slot. | ||

| Line 142: | Line 142: | ||

* 2x 512KiB EP1/EP2 ROM | * 2x 512KiB EP1/EP2 ROM | ||

* {{Chipname|PCM}} chip | * {{Chipname|PCM}} chip | ||

* LS139, LS08, | * LS139, LS08, LS74A | ||

[[Category:Cartridge boards]] | [[Category:Cartridge boards]] | ||

Latest revision as of 18:28, 15 August 2023

The only non-protected board that can bankswitch and use all V ROM space. Really common and very useful for homebrew stuff or converts.

Often used as the PROG board in Neo Print cartridges.

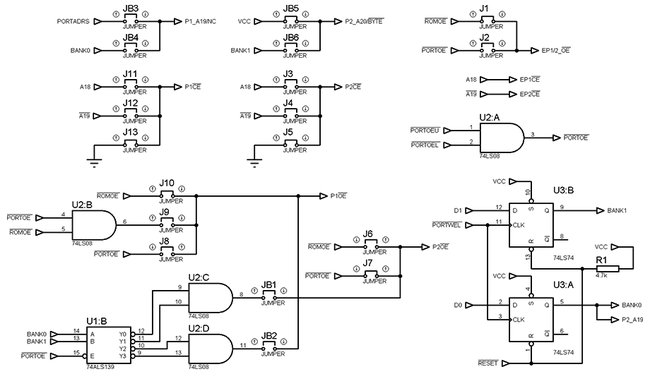

P ROMs configuration

EP ROMs /OE

| J1 | J2 |

|---|---|

| /ROMOE | /PORTOE |

P2 ROM /CE

| J3 | J4 | J5 |

|---|---|---|

| A18 | /A18 | GND (default) |

P2 ROM /OE

| J6 | J7 | JB1 |

|---|---|---|

| /ROMOE | /PORTOE (default) | /PORTOE, banks 0 and 1 |

P1 ROM /OE

| J8 | J9 | J10 | JB2 |

|---|---|---|---|

| /PORTOE | /PORTOE AND /ROMOE | /ROMOE (default) | /PORTOE, banks 2 and 3 |

P1 ROM /CE

| J11 | J12 | J13 |

|---|---|---|

| A18 | /A18 | GND (default) |

P1 ROM size

| JB3 | JB4 | Nothing |

|---|---|---|

| A19/NC is /PORTADRS (P1 is 16Mbit) | A19/NC is BANK0 (because reasons?) | P1 is 8Mbit |

P2 ROM size

| JB5 | JB6 |

|---|---|

| A20//BYTE is VCC (P2 is 16Mbit or less) | A20//BYTE is BANK1 (P2 is 32Mbit) |

The P1 ROM can be 4Mbit, 8Mbit or 16Mbit (27C400/27C800/27C160).

- ROMs can be halved and mapped to 0x000000~0x0FFFFF or 0x200000~0x2FFFFF.

- If P1 is 4Mbit or 8Mbit, then P2 can contain a bankswitched ROM (same type as P1 plus 27C322). P1 appears in 0x000000~0x0FFFFF. P2 bank appears in 0x200000~0x2FFFFF.

Bankswitching is done with the LS74. It's not needed if the game isn't banked. Any write to an odd address in the 0x200000~0x2FFFFF range will set the bank.

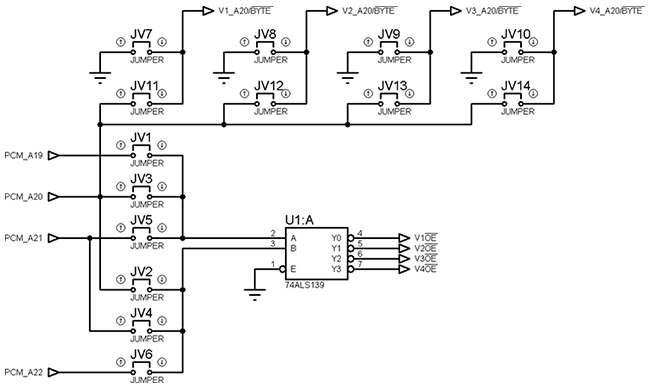

V ROMs configuration

There is a maximum of 4 V ROMs which can be 8Mbit, 16Mbit or 32Mbit (27C800/27C160/27C322) for a maximum total size of 4 * 4MiB = 16MiB.

A 4Mbit ROM can also be used, but only if there's one and only if it's in the last used slot.

The size of the largest V ROM is selected with a pair of jumpers on 6 spots (3 possible choices).

| Largest V ROM | Jumper set |

|---|---|

| 8Mbit (1MiB) | JV1+JV2 |

| 16Mbit (2MiB) | JV3+JV4 |

| 32Mbit (4MiB) | JV5+JV6 |

This pair of V ROM jumpers effectively choose a set of 2 of the PCM chip address outputs to input to the LS139, which will enable one out of the 4 V ROMs at a time.

The JV7 to JV14 jumpers need to be set according to the ROM types. If it's less than 32Mbit, the JV7/JV8/JV9/JV10 jumper needs to be set (ground). If it's 32Mbit, the JV11/JV12/JV13/JV14 needs to be set (A20). This is because 32Mbit chips have their /BYTE pin replaced by A20.

Other

The LS08 is used to AND the /PORTOEU and /PORTOEL signals to get /PORTOE.

- 4x 1/2/4MiB V ROMs

- 1/2MiB P1 ROM

- 1/2/4MiB P2 ROM

- 2x 512KiB EP1/EP2 ROM

- PCM chip

- LS139, LS08, LS74A