Graphics pipeline: Difference between revisions

Jump to navigation

Jump to search

mNo edit summary |

|||

| (2 intermediate revisions by one other user not shown) | |||

| Line 1: | Line 1: | ||

=First gen PRO chipset= | =First gen PRO chipset= | ||

*[[ | *[[LSPC-A0]] | ||

*[[PRO-B0]] | *[[PRO-B0]] | ||

*[[PRO-CT0]] | *[[PRO-CT0]] | ||

*[[ | *[[PRO-C0]] | ||

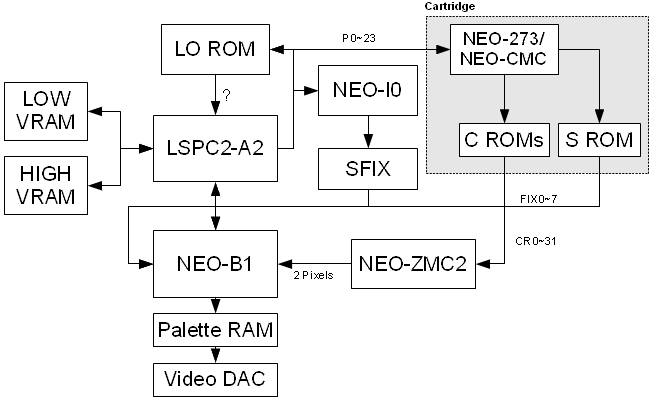

=Second gen chipset= | =Second gen chipset= | ||

| Line 17: | Line 17: | ||

*[[NEO-SFT]] new ZMC2 ? | *[[NEO-SFT]] new ZMC2 ? | ||

The sprite and fix DRAM bus can be switched between from NEO-OFC and the 68k bus for upload of graphics, thus allowing [[software rendering]]. | |||

=Last gen chipset= | =Last gen chipset= | ||

Latest revision as of 16:03, 22 April 2019

First gen PRO chipset

Second gen chipset

MVS

AES

CD gen chipset

The sprite and fix DRAM bus can be switched between from NEO-OFC and the 68k bus for upload of graphics, thus allowing software rendering.