68k: Difference between revisions

Jump to navigation

Jump to search

mNo edit summary |

mNo edit summary |

||

| (9 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

[[File:aes_68k.jpg|right|thumb|68000 CPU made by Toshiba in | [[File:aes_68k.jpg|right|thumb|68000 CPU made by Toshiba in SDIP package, as found on AES and some MVS boards.]] | ||

16bit big-endian CPU designed by Motorola, found in | The 68k (AKA 68000, MC68000, 68HC000) is a 16bit big-endian CPU designed by Motorola, found in all NeoGeo systems as the main processor. It runs at [[clock|12MHz]]. | ||

* Eight 32-bit data registers and eight 32-bit address registers | |||

* | |||

* 7 interrupt levels | * 7 interrupt levels | ||

* 56 instructions | * 56 instructions | ||

* 14 addressing modes | * 14 addressing modes | ||

=Related pages= | |||

See [[68k memory map]], [[68k interrupts]], and [[Links#68k programming|programming references]]. | See [[68k memory map]], [[68k interrupts]], [[wait cycle]], [[overclocking]], and [[Links#68k programming|programming references]]. | ||

== | =Pinouts= | ||

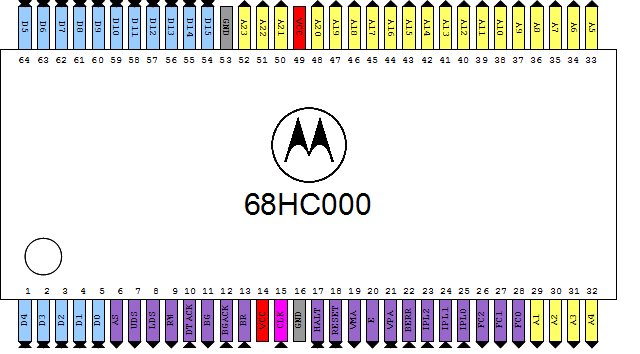

==SDIP== | |||

[[File:68000DIP.png]] | |||

[[File:68000DIP.odg]] | |||

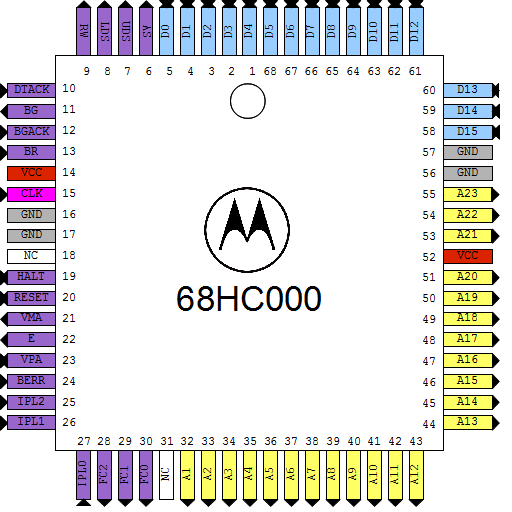

==PLCC== | |||

[[File:cd1_68k.jpg|right|thumb|The PLCC version.]] | |||

[[File:68000PLCC.png]] | |||

[[File:68000PLCC.odg]] | |||

=Datasheet= | |||

[[http://www.datasheetcatalog.org/datasheet/motorola/MC68HC000.pdf Original datasheet]] | |||

[[Category:Chips]] | [[Category:Chips]] | ||

[[Category: | [[Category:Base system]] | ||

Latest revision as of 18:58, 15 July 2023

The 68k (AKA 68000, MC68000, 68HC000) is a 16bit big-endian CPU designed by Motorola, found in all NeoGeo systems as the main processor. It runs at 12MHz.

- Eight 32-bit data registers and eight 32-bit address registers

- 7 interrupt levels

- 56 instructions

- 14 addressing modes

Related pages

See 68k memory map, 68k interrupts, wait cycle, overclocking, and programming references.