NEO-G0: Difference between revisions

Jump to navigation

Jump to search

m (direction) |

No edit summary |

||

| Line 1: | Line 1: | ||

[[File:Aes_g0.jpg|right|thumb | [[File:Aes_g0.jpg|right|thumb]] | ||

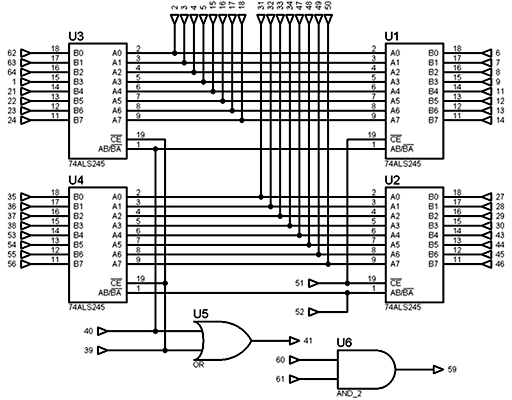

Quadruple 245 with OR and AND gates. Predecessor of [[NEO-BUF]]. | |||

=Internal logic= | |||

{| | |||

| | |||

[[File:neo-g0_internal.png]] | |||

| | |||

*Pin 51 is enable for MCD0~MCD15 | |||

*Pin 39 is enable for PALD0~PALD15 | |||

*Pin 40 is direction select for D0~D7 | |||

*Pin 52 is direction select for D8~D15 | |||

|} | |||

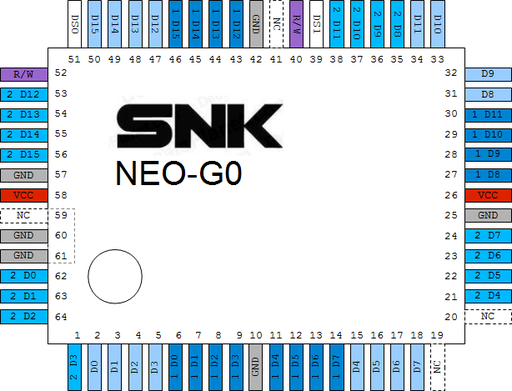

= | =AES pinout= | ||

[[File:Neo- | {| | ||

| | |||

[[File:Neo-g0_aes_pinout.png|512px|]] | |||

OpenOffice Draw file: [[File:neo- | OpenOffice Draw file: [[File:neo-g0_aes.odg]] | ||

| | |||

*D0~D15: [[68k]] data bus | |||

*PALD0~PALD7: Lower [[palette RAM]] data bus | |||

*PAUD0~PAUD7: Upper palette RAM data bus | |||

*MCD0~MCD15: [[Memory card]] data bus | |||

*D0~D15: 68k data bus | *PAL: Palette RAM address decode from [[PRO-C0]] | ||

* | *R/W: R/W from 68k | ||

* | *PALWE: Palette RAM /WE, output made from PAL OR R/W | ||

* | |||

* | *ROMOEL, ROMOEU: from PRO-C0 | ||

* | *ROMOE: Cartridge [[P ROM]] /OE, output made from ROMOEU AND ROMOEL | ||

**NEO-F0 - | |} | ||

** | |||

** | <div style="clear: left;"></div> | ||

* | |||

=MV2B @ J4 pinout= | |||

{| | |||

| | |||

[[File:Neo-g0_J4_pinout.png|512px]] | |||

OpenOffice Draw file: [[File:neo-g0_mv2b_J4.odg]] | |||

| | |||

*D0~D15: [[68k]] data bus | |||

*1D0~1D15: Slot 1 68k data bus | |||

*2D0~2D15: Slot 2 68k data bus | |||

*DS0,DS1: Slot 68k data enables from [[NEO-I0]] | |||

*R/W: R/W from 68k | |||

|} | |||

<div style="clear: left;"></div> | |||

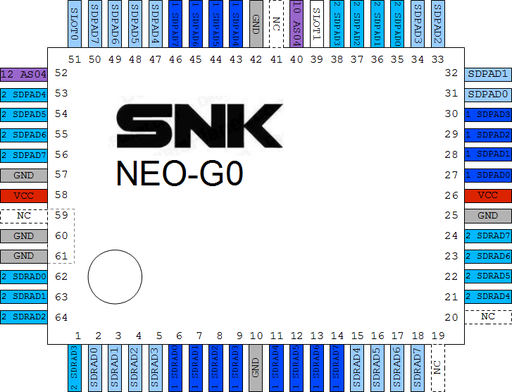

=MV2B @ J12 pinout= | |||

{| | |||

| | |||

[[File:Neo-g0_J12_pinout.png|512px]] | |||

OpenOffice Draw file: [[File:neo-g0_mv2b_J12.odg]] | |||

| | |||

*SDRAD0~SDRAD7: ADPCM-A data bus from [[YM2610]] | |||

*1SDRAD0~1SDRAD7: ADPCM-A data bus for slot 1 | |||

*2SDRAD0~2SDRAD7: ADPCM-A data bus for slot 2 | |||

*SDPAD0~SDPAD7: ADPCM-B data bus from YM2610 | |||

*1SDPAD0~1SDPAD7: ADPCM-B data bus for slot 1 | |||

*2SDPAD0~2SDPAD7: ADPCM-B data bus for slot 2 | |||

*10 AS04: negated /ROE from YM2610 | |||

*12 AS04: negated /POE from YM2610 | |||

*SLOT0, SLOT1: enables from [[NEO-F0]] | |||

|} | |||

<div style="clear: left;"></div> | |||

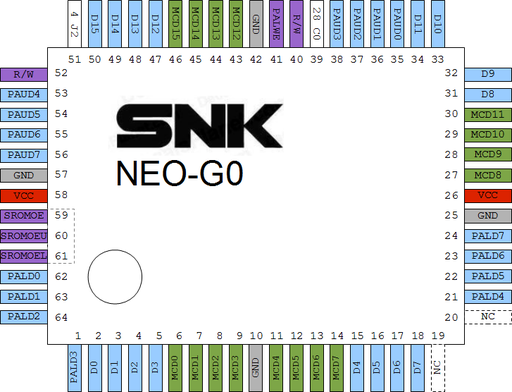

=MV2B @ C7 pinout= | |||

{| | |||

| | |||

[[File:Neo-g0_C7_pinout.png|512px]] | |||

OpenOffice Draw file: [[File:neo-g0_mv2b_C7.odg]] | |||

| | |||

Very similar connections with the one used in the AES. | |||

*D0~D15: [[68k]] data bus | |||

*PALD0~PALD7: Lower [[palette RAM]] data bus | |||

*PAUD0~PAUD7: Upper palette RAM data bus | |||

*MCD0~MCD15: [[Memory card]] data bus | |||

*28 C0 (PAL ?): from [[PRO-C0]] | |||

*4 J2: ? | |||

*R/W: R/W from 68k | |||

*SROMOEL, SROMOEU: from PRO-C0, BIOS byte /OE | |||

*ROMOE: [[BIOS]] ROM /OE, output made from SROMOEU AND SROMOEL | |||

|} | |||

<div style="clear: left;"></div> | |||

[[Category:Chips]] | [[Category:Chips]] | ||

Revision as of 18:23, 13 August 2012

Quadruple 245 with OR and AND gates. Predecessor of NEO-BUF.

Internal logic

|

AES pinout

|

OpenOffice Draw file: File:Neo-g0 aes.odg |

|

MV2B @ J4 pinout

|

OpenOffice Draw file: File:Neo-g0 mv2b J4.odg |

|

MV2B @ J12 pinout

|

OpenOffice Draw file: File:Neo-g0 mv2b J12.odg |

|

MV2B @ C7 pinout

|

OpenOffice Draw file: File:Neo-g0 mv2b C7.odg |

Very similar connections with the one used in the AES.

|