NEO-G0: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

mNo edit summary |

||

| Line 16: | Line 16: | ||

=AES pinout= | =AES pinout= | ||

Palette RAM and memory card access. Palette RAM /WE and P1 ROM /OE generation. | |||

{| | {| | ||

| Line 28: | Line 30: | ||

*MCD0~MCD15: [[Memory card]] data bus | *MCD0~MCD15: [[Memory card]] data bus | ||

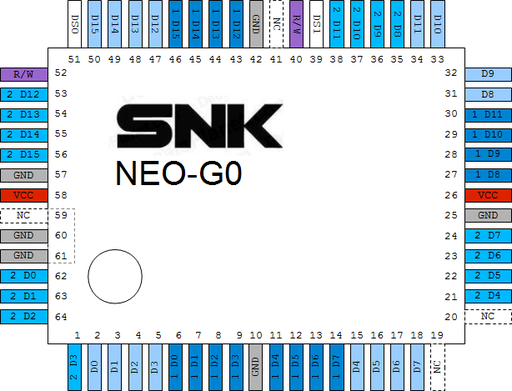

*PAL: Palette RAM address decode from [[ | *PAL: Palette RAM address decode from [[NEO-C1]] | ||

*R/W: R/W from 68k | *R/W: R/W from 68k | ||

*PALWE: Palette RAM /WE, output made from PAL OR R/W | *PALWE: Palette RAM /WE, output made from PAL OR R/W | ||

| Line 39: | Line 41: | ||

=MV2B @ J4 pinout= | =MV2B @ J4 pinout= | ||

68k data bus access for both slots. | |||

{| | {| | ||

| Line 58: | Line 62: | ||

=MV2B @ J12 pinout= | =MV2B @ J12 pinout= | ||

ADPCM buses access for both slots. | |||

{| | {| | ||

| Line 82: | Line 88: | ||

=MV2B @ C7 pinout= | =MV2B @ C7 pinout= | ||

Palette RAM and memory card access. Palette RAM /WE and BIOS /OE generation. | |||

{| | {| | ||

| Line 95: | Line 103: | ||

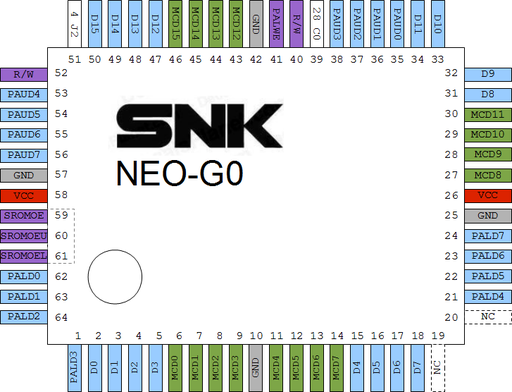

*MCD0~MCD15: [[Memory card]] data bus | *MCD0~MCD15: [[Memory card]] data bus | ||

*28 C0 (PAL ?): from [[PRO-C0]] | *28 C0 (PAL ?):Palette RAM address decode from [[PRO-C0]] | ||

*R/W: R/W from 68k | *R/W: R/W from 68k | ||

*PALWE: Palette RAM /WE, output made from PAL OR R/W | |||

*SROMOEL, SROMOEU: from PRO-C0, BIOS byte /OE | *SROMOEL, SROMOEU: from PRO-C0, BIOS byte /OE | ||

Revision as of 19:57, 13 August 2012

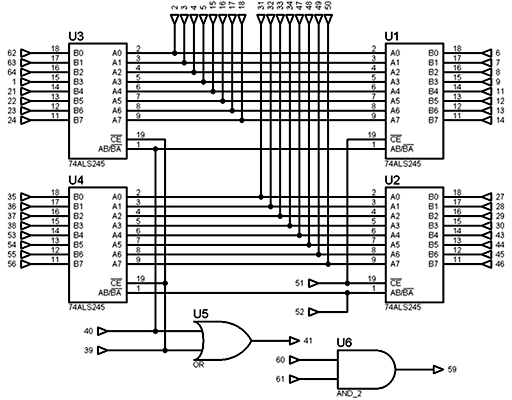

Quadruple 245 with OR and AND gates. Predecessor of NEO-BUF.

Internal logic

|

AES pinout

Palette RAM and memory card access. Palette RAM /WE and P1 ROM /OE generation.

|

OpenOffice Draw file: File:Neo-g0 aes.odg |

|

MV2B @ J4 pinout

68k data bus access for both slots.

|

OpenOffice Draw file: File:Neo-g0 mv2b J4.odg |

|

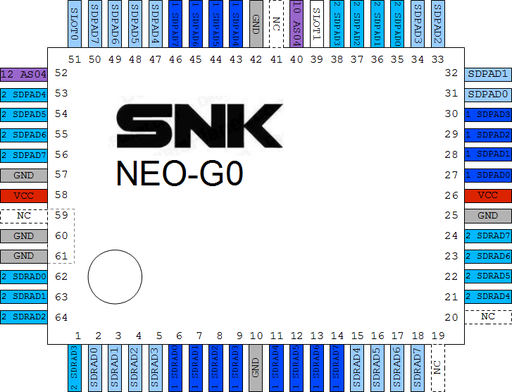

MV2B @ J12 pinout

ADPCM buses access for both slots.

|

OpenOffice Draw file: File:Neo-g0 mv2b J12.odg |

|

MV2B @ C7 pinout

Palette RAM and memory card access. Palette RAM /WE and BIOS /OE generation.

|

OpenOffice Draw file: File:Neo-g0 mv2b C7.odg |

Very similar connections with the one used in the AES.

|