Reset: Difference between revisions

mNo edit summary |

No edit summary |

||

| (One intermediate revision by the same user not shown) | |||

| Line 1: | Line 1: | ||

The NeoGeo reset | The NeoGeo reset signal path can be confusing. The involved signals are: | ||

* {{Sig|VCCON|VCCON}} (MVS only) or {{Sig|RST|RST}} (home console reset button and [[PST518B]]). | |||

* {{Sig|RESET|RESET|N}}: Main, clean reset signal. | |||

* {{Sig|RESETP|RESETP|N}}: Phase sync pulse for {{Chipname|NEO-D0}}. | |||

==Path== | ==Path== | ||

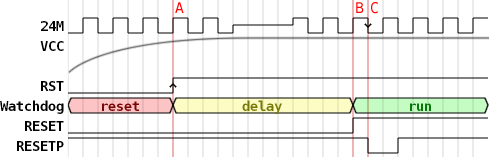

The reset | The reset process starts when the open collector VCCON/RST line is set low by the PST518B reset generator, or the reset button. As long as this line is low, {{Chipname|NEO-B1}} keeps its RESET output low. When it goes high again, it lets the [[watchdog]] timer keep RESET low during 8 more frames. This ensures that RESET stays low for at least ~135ms. When RESET goes high, {{Chipname|LSPC2-A2}} outputs a 1mclk-long negative pulse on RESETP to synchronize {{Chipname|NEO-D0}}'s other clock outputs. | ||

[[File:resets.png]] | |||

* A: The VCC voltage is high enough, the PST518B lets go of the RST line. The pull-up makes it go high. The watchdog timer keeps RESET low for 8 frames. | |||

* B: The watchdog reset timer expires, NEO-B1 lets go of RESET. The pull-up makes it go high. | |||

* C: LSPC sees the rising edge on RESET, generates the RESETP negative pulse (synchronized to falling edges of 24M). | |||

=Notes= | |||

==Video sync== | |||

LSPC still generates a video sync signal even when RESET is low. This is needed because NEO-B1 uses the {{Sig|BNKB|BNKB}} signal to time the reset period, which depends on the video sync. This can be observed when the home console's reset button is kept pressed: a valid black picture is still generated. The picture only "jumps" when the button is released because the RESETP pulse causes the sync generator to be reset. | |||

== | ==68k CPU== | ||

To reset the {{Chipname|68k}}, both the HALT and RESET lines must be held low for at least 100ms. Since they're bidirectional pins, they aren't tied together. Internally, NEO-B1 drives both of its RESET and HALT outputs from the same signal, but they're kept separate to prevent HALT driving RESET in case of a bus fault. See the 68k manual for details. | |||

RESET | Note that the 68k RESET instruction will only make the RESET line go low: it will reset everything '''except''' the 68k. | ||

The RESET and HALT lines '''must''' pulled high by 4.7kohm resistors. | |||

[[Category:Base system]] | [[Category:Base system]] | ||

Latest revision as of 00:24, 22 June 2018

The NeoGeo reset signal path can be confusing. The involved signals are:

- VCCON (MVS only) or RST (home console reset button and PST518B).

- RESET: Main, clean reset signal.

- RESETP: Phase sync pulse for NEO-D0.

Path

The reset process starts when the open collector VCCON/RST line is set low by the PST518B reset generator, or the reset button. As long as this line is low, NEO-B1 keeps its RESET output low. When it goes high again, it lets the watchdog timer keep RESET low during 8 more frames. This ensures that RESET stays low for at least ~135ms. When RESET goes high, LSPC2-A2 outputs a 1mclk-long negative pulse on RESETP to synchronize NEO-D0's other clock outputs.

- A: The VCC voltage is high enough, the PST518B lets go of the RST line. The pull-up makes it go high. The watchdog timer keeps RESET low for 8 frames.

- B: The watchdog reset timer expires, NEO-B1 lets go of RESET. The pull-up makes it go high.

- C: LSPC sees the rising edge on RESET, generates the RESETP negative pulse (synchronized to falling edges of 24M).

Notes

Video sync

LSPC still generates a video sync signal even when RESET is low. This is needed because NEO-B1 uses the BNKB signal to time the reset period, which depends on the video sync. This can be observed when the home console's reset button is kept pressed: a valid black picture is still generated. The picture only "jumps" when the button is released because the RESETP pulse causes the sync generator to be reset.

68k CPU

To reset the 68k, both the HALT and RESET lines must be held low for at least 100ms. Since they're bidirectional pins, they aren't tied together. Internally, NEO-B1 drives both of its RESET and HALT outputs from the same signal, but they're kept separate to prevent HALT driving RESET in case of a bus fault. See the 68k manual for details.

Note that the 68k RESET instruction will only make the RESET line go low: it will reset everything except the 68k.

The RESET and HALT lines must pulled high by 4.7kohm resistors.