Reset: Difference between revisions

mNo edit summary |

m (Cleaning, links) |

||

| Line 1: | Line 1: | ||

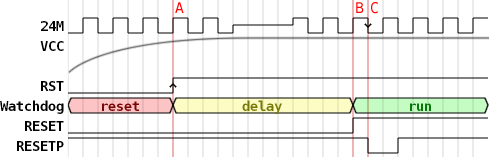

VCCON (MVS) or RST (AES reset button | The NeoGeo reset "signal path" can be confusing. The involved signals are {{Sig|VCCON|VCCON}} (MVS only) or {{Sig|RST|RST}} (AES reset button and [[PST518B]]), {{Sig|RESET|RESET}} (main, clean reset signal), and {{Sig|RESETP|RESETP}} (reset release pulse for {{Chipname|NEO-D0}}). | ||

==Path== | |||

The reset trigger starts with signals VCCON or RST, which come from either the reset button or the PST518B reset generator. It goes to {{Chipname|NEO-B1}}, which sets its internal [[watchdog]] timer to generate a long enough negative pulse on RESET. {{Chipname|LSPC2-A2}} synchronizes the rising edge to the main clock's falling edge to output a 1mclk negative pulse on RESETP. | |||

VCCON, RST and RESET seem to be open-collector lines. RESET is pulled high by a 4.7k resistor. | |||

[[File:resets.png]] | [[File:resets.png]] | ||

==Notes== | |||

RESET might be synchronized with a clock reaching B1 (1MB ? 6MB ?). | RESET might be synchronized with a clock reaching B1 (1MB ? 6MB ?). | ||

Revision as of 18:23, 22 June 2016

The NeoGeo reset "signal path" can be confusing. The involved signals are VCCON (MVS only) or RST (AES reset button and PST518B), RESET (main, clean reset signal), and RESETP (reset release pulse for NEO-D0).

Path

The reset trigger starts with signals VCCON or RST, which come from either the reset button or the PST518B reset generator. It goes to NEO-B1, which sets its internal watchdog timer to generate a long enough negative pulse on RESET. LSPC2-A2 synchronizes the rising edge to the main clock's falling edge to output a 1mclk negative pulse on RESETP.

VCCON, RST and RESET seem to be open-collector lines. RESET is pulled high by a 4.7k resistor.

Notes

RESET might be synchronized with a clock reaching B1 (1MB ? 6MB ?).

RESETP is triggered by the watchdog also (since it asserts RESET).