NEO-G0: Difference between revisions

Jump to navigation

Jump to search

m (BIOS -> system ROM) |

m (→Internal logic) |

||

| (6 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

{{ChipInfo | |||

|picture=Aes_g0.jpg | |||

|pkg=QFP64R | |||

|manu=fujitsu | |||

|date=1992 ? | |||

|gates= | |||

|used_on={{PCB|MV2B}} ... | |||

}} | |||

Quadruple 245 with OR and AND gates. Predecessor of | Quadruple 245 with additional OR and AND gates. Predecessor of {{Chipname|NEO-BUF}}. | ||

=Internal logic= | =Internal logic= | ||

Schematic is wrong: A and B sides are flipped ! | |||

{| | {| | ||

| Line 15: | Line 24: | ||

|} | |} | ||

=AES | =Pinouts= | ||

==AES== | |||

Palette RAM and memory card access. Palette RAM /WE and P1 ROM /OE generation. | Palette RAM and memory card access. Palette RAM /WE and P1 ROM /OE generation. | ||

| Line 21: | Line 32: | ||

{| | {| | ||

| | | | ||

{{Pinout|NEO-G0_aes|512}} | |||

| | | | ||

*D0~D15: [[68k]] data bus | *D0~D15: [[68k]] data bus | ||

| Line 40: | Line 49: | ||

<div style="clear: left;"></div> | <div style="clear: left;"></div> | ||

=MV2B | ==MV2B== | ||

= | |||

<gallery> | |||

File:Neo-g0_J4_pinout.png|J4: 68k data bus access for both slots. DS0,DS1: Slot 68k data enables from [[NEO-I0]]. OpenOffice Draw file: [[File:neo-g0_mv2b_J4.odg]] | |||

File:Neo-g0_J12_pinout.png|J12: ADPCM buses access for both slots. 10 AS04: negated /ROE from YM2610, 12 AS04: negated /POE from YM2610. SLOT0, SLOT1: enables from [[NEO-F0]]. OpenOffice Draw file: [[File:neo-g0_mv2b_J12.odg]] | |||

File:Neo-g0_C7_pinout.png|B7: Palette RAM and memory card access. Palette RAM /WE and System ROM /OE generation. 28 C0 (PAL ?):Palette RAM address decode from [[PRO-C0]]. OpenOffice Draw file: [[File:neo-g0_mv2b_C7.odg]] | |||

</gallery> | |||

| | |||

Palette RAM and memory card access. Palette RAM /WE and System ROM /OE generation. | |||

[[Category:Chips]] | [[Category:Chips]] | ||

Latest revision as of 19:35, 2 May 2020

| |

| Package | QFP64R |

| Manufacturer | |

| First use | 1992 ? |

| Used on | MV2B ... |

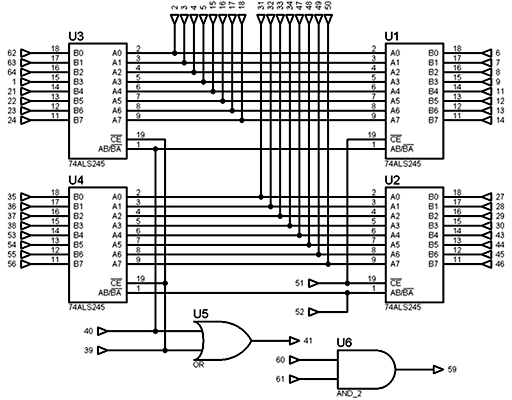

Quadruple 245 with additional OR and AND gates. Predecessor of NEO-BUF.

Internal logic

Schematic is wrong: A and B sides are flipped !

|

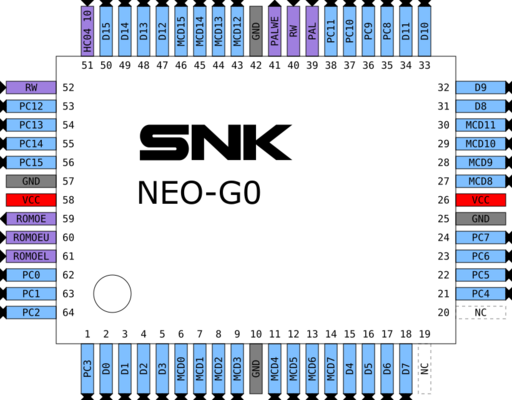

Pinouts

AES

Palette RAM and memory card access. Palette RAM /WE and P1 ROM /OE generation.

|

MV2B

-

J4: 68k data bus access for both slots. DS0,DS1: Slot 68k data enables from NEO-I0. OpenOffice Draw file: File:Neo-g0 mv2b J4.odg

-

J12: ADPCM buses access for both slots. 10 AS04: negated /ROE from YM2610, 12 AS04: negated /POE from YM2610. SLOT0, SLOT1: enables from NEO-F0. OpenOffice Draw file: File:Neo-g0 mv2b J12.odg

-

B7: Palette RAM and memory card access. Palette RAM /WE and System ROM /OE generation. 28 C0 (PAL ?):Palette RAM address decode from PRO-C0. OpenOffice Draw file: File:Neo-g0 mv2b C7.odg