Category:Chips: Difference between revisions

Jump to navigation

Jump to search

m (Pinout filenames) |

m (Pinout filenames) |

||

| Line 105: | Line 105: | ||

* Coin I/O | * Coin I/O | ||

* [[Memory_mapped_registers#System_registers|System register]] | * [[Memory_mapped_registers#System_registers|System register]] | ||

* [[Wait | * [[Wait cycle]] generator | ||

|Some MVS | |Some MVS | ||

|[[File: | |[[File:NEO-DCR_pinout.png|x128px|center]] | ||

|- | |- | ||

|[[File:aes_e0.jpg|x128px|center]] | |[[File:aes_e0.jpg|x128px|center]] | ||

| Line 115: | Line 115: | ||

*Buffer/driver | *Buffer/driver | ||

|Some AES, some MVS | |Some AES, some MVS | ||

|[[File: | |[[File:NEO-E0_pinout.png|x128px|center]] | ||

|- | |- | ||

|[[File:mvs_f0.jpg|x128px|center]] | |[[File:mvs_f0.jpg|x128px|center]] | ||

| Line 125: | Line 125: | ||

*Slot selection | *Slot selection | ||

|Some MVS | |Some MVS | ||

|[[File: | |[[File:NEO-F0_pinout.png|x128px|center]] | ||

|- | |- | ||

|[[File:aes_g0.jpg|x128px|center]] | |[[File:aes_g0.jpg|x128px|center]] | ||

| Line 135: | Line 135: | ||

*[[68k]] data bus buffer | *[[68k]] data bus buffer | ||

|All AES, some MVS ? | |All AES, some MVS ? | ||

|[[File: | |[[File:NEO-G0_aes_pinout.png|x128px|center]] | ||

|- | |- | ||

|[[File:cd2_grc.jpg|x128px|center]] | |[[File:cd2_grc.jpg|x128px|center]] | ||

| Line 141: | Line 141: | ||

|Graphics chip | |Graphics chip | ||

|All CD1, all CD2 | |All CD1, all CD2 | ||

| | |[[File:Neo-grc_pinout.png|x128px|center]] | ||

|- | |- | ||

|[[File:neo-grc2-f.jpg|x128px|center]] | |[[File:neo-grc2-f.jpg|x128px|center]] | ||

| Line 161: | Line 161: | ||

*Coin counter and lockout outputs | *Coin counter and lockout outputs | ||

|Some MVS | |Some MVS | ||

|[[File: | |[[File:NEO-I0_pinout.png|x128px|center]] | ||

|- | |- | ||

|[[File:cd2_mga.jpg|x128px|center]] | |[[File:cd2_mga.jpg|x128px|center]] | ||

| Line 190: | Line 190: | ||

* 68k/Z80 communication latches and interrupt generation | * 68k/Z80 communication latches and interrupt generation | ||

|Some MVS, All [[Neo Print]]s | |Some MVS, All [[Neo Print]]s | ||

|[[File: | |[[File:NEO-SDR_pinout.png|x128px|center]] | ||

|- | |- | ||

|[[File:cd2_sft.jpg|x128px|center]] | |[[File:cd2_sft.jpg|x128px|center]] | ||

| Line 228: | Line 228: | ||

|Z80 Memory Controller | |Z80 Memory Controller | ||

|Cartridges | |Cartridges | ||

|[[File: | |[[File:NEO-ZMC_pinout.png|x128px|center]] | ||

|- | |- | ||

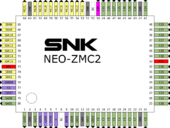

|[[File:mvs_zmc2.jpg|x128px|center]] | |[[File:mvs_zmc2.jpg|x128px|center]] | ||

| Line 236: | Line 236: | ||

*Sprite tile serializer | *Sprite tile serializer | ||

|AES carts, some MVS | |AES carts, some MVS | ||

|[[File: | |[[File:NEO-ZMC2_pinout.png|x128px|center]] | ||

|- | |- | ||

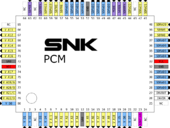

|[[File:crt_pcm.jpg|x128px|center]] | |[[File:crt_pcm.jpg|x128px|center]] | ||

| Line 244: | Line 244: | ||

*[[V ROM]] multiplexer | *[[V ROM]] multiplexer | ||

|Cartridges | |Cartridges | ||

|[[File: | |[[File:PCM_pinout.png|x128px|center]] | ||

|- | |- | ||

|[[File:pstg-snk.jpg|x128px|center]] | |[[File:pstg-snk.jpg|x128px|center]] | ||

| Line 259: | Line 259: | ||

*Z80 latch | *Z80 latch | ||

|Some AES, some MVS | |Some AES, some MVS | ||

|[[File: | |[[File:PRO-B0_pinout.png|x128px|center]] | ||

|- | |- | ||

|[[File:mvs_pro-c0.jpg|x128px|center]] | |[[File:mvs_pro-c0.jpg|x128px|center]] | ||

| Line 269: | Line 269: | ||

*Palette arbiter | *Palette arbiter | ||

|Some AES, some MVS | |Some AES, some MVS | ||

|[[File: | |[[File:PRO-C0_pinout.png|x128px|center]] | ||

|- | |- | ||

|[[File:mvs_pro-ct0.jpg|x64px|center]] | |[[File:mvs_pro-ct0.jpg|x64px|center]] | ||

Revision as of 01:55, 8 July 2018

Todo:

- Chips with (manufacturer name) need ChipInfo templates on their pages

- LC98000, LSPC-A0, PRO-C0, PRO-B0, NEO-GRC2, NEO-MGA pinouts

- RAMs (VRAM, 68k, Z80)

| Picture | Reference | Description | Found in | Pinout |

|

LSPC-A0 | First generation graphics chip | Some AES, some MVS |  |

|

LSPC2-A2 | Second generation graphics chip | Some AES, some MVS |  |

|

LSPC2-A3 | Revision of the second generation graphics chip | Some MVS |  |

|

NEO-244 | Some MVS | ||

|

NEO-253 | Quint 74HC253, 4-to-1 multiplexers | Some MVS |  |

|

NEO-257 | Quad 74HC257, 2-to-1 multiplexers | Some MVS |  |

|

NEO-273 | C and S ROM address latches | Cartridges |  |

|

NEO-B1 | Second generation graphics chip

|

Some AES, some MVS |  |

|

NEO-BUF | Dual 8-bit bidirectional buffer | CD1, CD2, some late MVS |  |

|

NEO-C1 |

|

Some AES, some MVS |  |

|

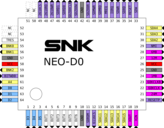

NEO-D0 |

|

All AES ?, some MVS |  |

|

NEO-CMC |

|

Some cartridges |  |

|

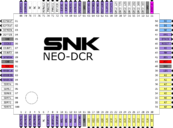

NEO-DCR-T |

|

Some MVS |  |

|

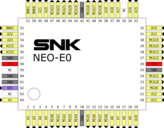

NEO-E0 |

|

Some AES, some MVS |  |

|

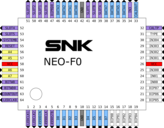

NEO-F0 |

|

Some MVS |  |

|

NEO-G0 |

Quad 245 bidirectional buffer.

|

All AES, some MVS ? |  |

|

NEO-GRC | Graphics chip | All CD1, all CD2 |  |

|

NEO-GRC2-F (Fujitsu) | Graphics chip | All CDZ ?, Some MVS |  |

|

NEO-GRZ (Fujitsu) | All-in-one GPU | ROM-only | |

|

NEO-I0 | Multi-purpose MVS specific chip.

|

Some MVS |  |

|

NEO-MGA NEO-MGA-T NEO-MGA-T2 |

CD unit interface, latches, address decoding ? | All CD1, all CD2, all CDZ, some MVS |  |

|

NEO-OFC (Fujitsu) | Graphics chip | All CD1, all CD2 | |

|

NEO-PCM2 (Fujitsu) | ROM-only boards |  | |

|

NEO-SDR-T |

|

Some MVS, All Neo Prints |  |

|

NEO-SFT (Fujitsu) | Graphics related | All CD1, all CD2 | |

|

NEO-SUD | Z80 subsystem controler | All CD1, all CD2 | |

|

NEO-VOC (Yamaha) | PCM memory handler | All CD1, all CD2 | |

|

NEO-YSA (Yamaha) | Audio subsystem chip | Some CD2 | |

|

NEO-YSA2 (Yamaha) | Complete audio subsystem chip

|

All CDZ ?, All ROM-only | |

|

NEO-ZMC | Z80 Memory Controller | Cartridges |  |

|

NEO-ZMC2 |

|

AES carts, some MVS |  |

|

PCM |

|

Cartridges |  |

|

PSTG-SNK |

Neo Print GPU. |

||

|

PRO-B0 | First generation

|

Some AES, some MVS |  |

|

PRO-C0 | First generation

|

Some AES, some MVS |  |

|

PRO-CT0 | C ROM character serializer and multiplexer | Some AES carts, some MVS |  |

|

NEO-PVC (Fujitsu) | P ROM decryption chip | ||

|

NEO-SMA | P ROM decryption chip |

Other chips

| Picture | Reference | Description | Found in | ||||

| AES | MVS | CD1 | CD2 | CDZ | |||

|

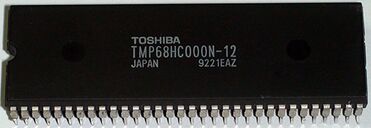

68HC000 (Toshiba DIP64) | 16bit CPU | All | Some | |||

|

68HC000 (Motorola PLCC68) | Some | All | All | All | ||

|

Sony CXA1145 | RGB encoder | All | ||||

|

Sony CXA1645 | ? | All | ? | |||

|

Hitachi HD6301 (DIP40) | Microcontroller | Multiplayer cartridges | ||||

|

Sanyo LC78815 | Stereo DAC | ? | All | |||

|

Sanyo LC89515 | CD host and error corrector | All | All | ? | ||

|

Sanyo LC8953 | PUPPET | All | Some | ? | ||

|

Sanyo LC98000 | PUPPET replacement | Some | ? | |||

|

NEC UPD4990 | Real Time Clock | All | ||||

|

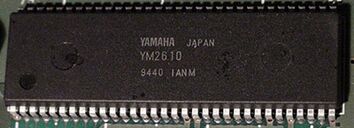

Yamaha YM2610 | Sound synthesizer | All | All | All | Some | |

|

Yamaha YM3016 | Audio DAC | All | All | All | Some | |

|

Zilog z80 (DIP40) | 8bit CPU | All | Some | |||

|

Toshiba z80 (SOIC) | Some | All | All | All | ||

Memory chips

| Picture | Reference | Description | Found in |

|

LO | Shrink lookup ROM | All systems |

|

SP-S2 | MVS System ROM | MVS systems |

|

SM1 | Embedded sound driver ROM | |

|

SFIX ROM | Embedded Fix ROM | |

|

NEO-EP0 | AES System ROM | AES systems |

| Picture needed | TOP-SP1-1 | CD2 System ROM | Top loading CD systems (LC8953 versions) |

| Picture needed | TOP-SP1-2 | CD2 System ROM | Top loading CD systems (LC98000 versions) |

| FRONT-SP1 | CD1 System ROM | Front loading CD systems |

Pages in category "Chips"

The following 108 pages are in this category, out of 108 total.

6

C

D

H

L

N

- NEO-244

- NEO-253

- NEO-257

- NEO-273

- NEO-B1

- NEO-BUF

- NEO-C1

- NEO-CDA board

- NEO-CDD board

- NEO-CMC

- NEO-D0

- NEO-DCR-T

- NEO-E0

- NEO-EP0

- NEO-F0

- NEO-FTC1B board

- NEO-G0

- NEO-GRC

- NEO-GRC2

- NEO-GRZ

- NEO-HYCS

- NEO-I0

- NEO-MGA

- NEO-MGA-T

- NEO-OFC

- NEO-PCM2

- NEO-PVC

- NEO-SDR-T

- NEO-SFT

- NEO-SMA

- NEO-SUD

- NEO-VOC

- NEO-YSA

- NEO-YSA2

- NEO-ZMC

- NEO-ZMC2

- NGPC flash board

- NJM2066